Xhyper剖析[1]--ARM64基础知识

2.1 寄存器

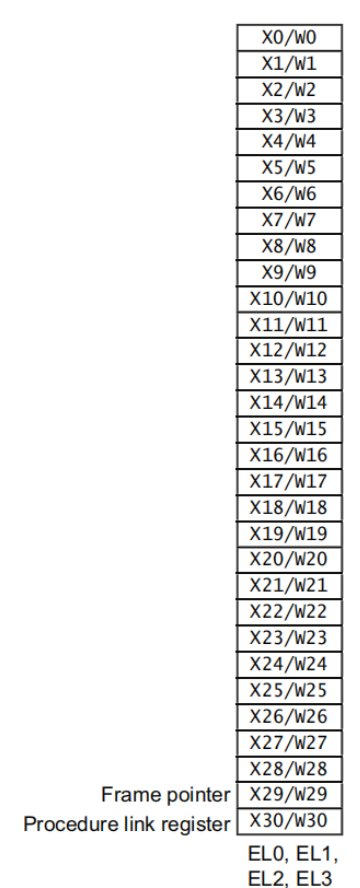

通用寄存器

AArch64执行状态提供了32个在任何时间任何特权级下都可访问的64位的通用寄存器。 每个寄存器都有64位宽,它们通常被称为寄存器X0-X30。

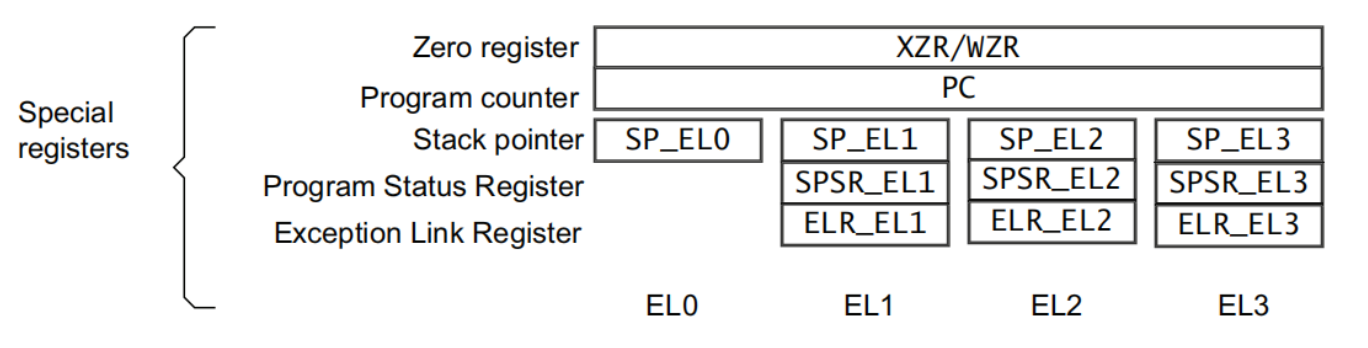

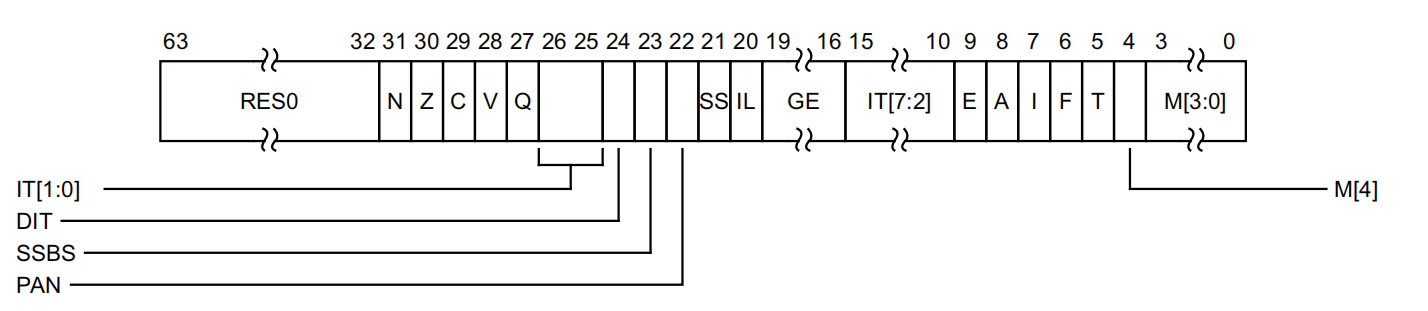

SPSR

当异常发生时,处理器状态将保存在相关的程序状态保存寄存器(SPSR)中,

| M[3:0] | Binary | 状态 | 描述 |

|---|---|---|---|

| 0 | 0x0 | EL0t | EL0(用户态),Thread 模式,使用 SP_EL0(共享栈),AArch64。 |

| 0 | 0x4 | EL1t | EL1(内核态),Thread 模式,使用 SP_EL0(共享栈),AArch64。 |

| 0 | 0x5 | EL1h | EL1(内核态),Handler 模式,使用 SP_EL1(专用栈),AArch64。 |

| 0 | 0x8 | EL2t | EL2(Hypervisor),Thread 模式,使用 SP_EL0(共享栈),AArch64。 |

| 0 | 0x9 | EL2h | EL2(Hypervisor),Handler 模式,使用 SP_EL2(专用栈),AArch64。 |

| 0 | 0xC | EL3t | EL3(Secure Monitor),Thread 模式,使用 SP_EL0(共享栈),AArch64。 |

| 0 | 0xD | EL3h | EL3(Secure Monitor),Handler 模式,使用 SP_EL3(专用栈),AArch64。 |

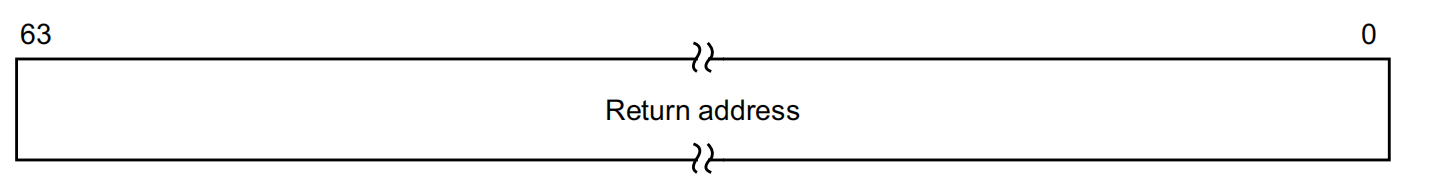

ELR_ELx

- 异常返回地址存储寄存器

VTCR_EL2

Virtualization Translation Control Register (EL2),用于在虚拟化环境中(即 EL2,Hypervisor 模式)控制虚拟机的地址转换和内存管理。它主要用于配置虚拟机 (VM) 的第二阶段 (Stage-2) 地址转换,管理从虚拟地址到物理地址的映射。

https://dflund.se/~getz/ARM/SysReg/AArch64-vtcr_el2.html

- **T0SZ (**Bits [5:0])

- 指定输入地址范围的大小,表示虚拟机在 Stage-2 转换中使用的虚拟地址范围。

- 值为 2^(64-T0SZ),表示输入地址的位数。例如:

- T0SZ = 24 表示 40 位虚拟地址 (2^(64-24) = 2^40)。

- 用于定义虚拟机可访问的虚拟地址空间大小。

- **SL0 (**Bits [7:6])

- 指定 Stage-2 转换表的起始级别 (Starting Level),决定转换表查找的起始层级。

- 例如:

- 0b00:从 Level 0 开始

- 0b01:从 Level 1 开始

- 0b10:从 Level 2 开始

- 与页面大小和地址范围相关。

- **IRGN0 (**Bits [9:8])

- 控制 Stage-2 转换表的 Inner Cacheability 属性:

- 0b00:Non-cacheable

- 0b01:Write-Back, Write-Allocate

- 0b10:Write-Through, No Write-Allocate

- 0b11:Write-Back, No Write-Allocate

- 控制 Stage-2 转换表的 Inner Cacheability 属性:

- **ORGN0 (**Bits [11:10])

- 控制 Stage-2 转换表的 Outer Cacheability 属性,类似 IRGN0。

- **SH0 (**Bits [13:12])

- 控制 Stage-2 转换表的 Shareability 属性:

- 0b00:Non-shareable

- 0b01:保留

- 0b10:Outer Shareable

- 0b11:Inner Shareable

- 控制 Stage-2 转换表的 Shareability 属性:

- **TG0 (**Bits [15:14])

- 指定 Stage-2 转换的页面粒度 (Translation Granule):

- 0b00:4KB 页面

- 0b01:16KB 页面

- 0b10:64KB 页面

- 0b11:保留

- 指定 Stage-2 转换的页面粒度 (Translation Granule):

- PS **(**Bits [19:16])

- 指定 Stage-2 转换支持的物理地址大小 (Physical Address Size):

- 0b000:32 位

- 0b001:36 位

- 0b010:40 位

- 0b011:42 位

- 0b100:44 位

- 0b101:48 位

- 0b110:52 位

- 指定 Stage-2 转换支持的物理地址大小 (Physical Address Size):

- VS (Bit [30])

- 表示是否支持 8 位或 16 位 VMID (Virtual Machine Identifier):

- 0b0:8 位 VMID

- 0b1:16 位 VMID

- 与 ID_AA64MMFR0_EL1 的 VMIDBits 字段相关。

- 表示是否支持 8 位或 16 位 VMID (Virtual Machine Identifier):

- RES1 (某些位)

- 某些位是保留位,必须写入 1(RES1),以确保兼容性。

- NSW (Non-Secure World)

- 指示 Stage-2 转换是否将内存访问视为非安全(Non-Secure)世界的一部分。

NSW = 0:

Stage-2 转换的内存访问被视为安全(Secure)世界的一部分。

适用于运行在安全状态下的虚拟机(VM)或需要访问安全内存的场景。

NSW = 1:

Stage-2 转换的内存访问被视为非安全(Non-Secure)世界的一部分。

适用于运行在非安全状态下的虚拟机,这是虚拟化环境中更常见的情况(例如运行普通操作系统如 Linux 的虚拟机)。

非安全访问不会触发安全监视器(Secure Monitor)的干预。

- NSA (Non-Secure Access)

NSA = 0:

Stage-2 转换的内存访问不会被强制标记为非安全访问。

内存访问的安全属性由其他控制机制(例如 NSW 位或 Stage-2 转换表中的描述符)决定。

NSA = 1:

Stage-2 转换的内存访问被强制标记为非安全(Non-Secure)访问。

这意味着即使虚拟机运行在安全上下文中,其内存访问也会被视为非安全世界的访问,通常用于确保虚拟机的内存操作不会意外访问安全内存。

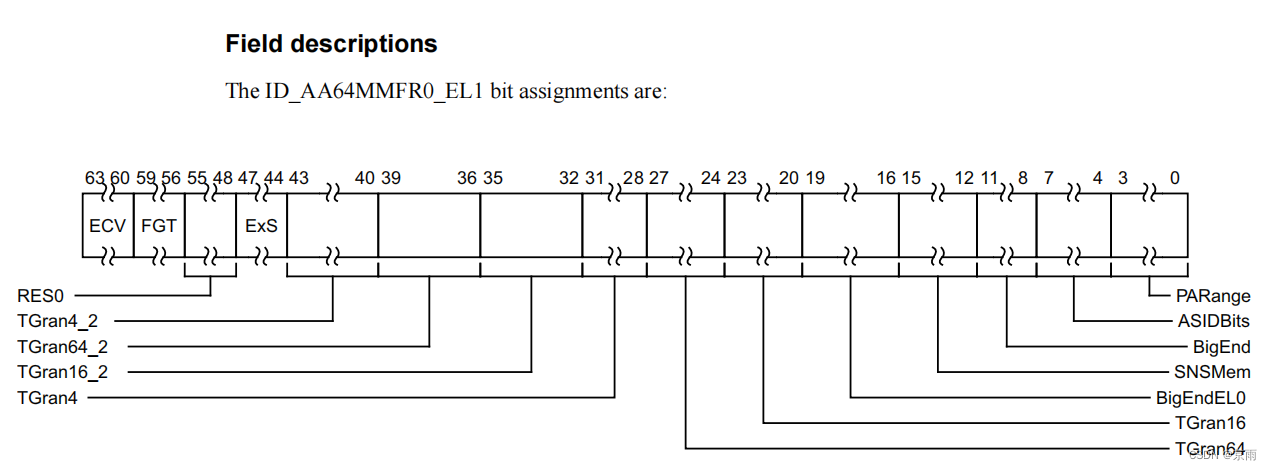

ID_AA64MMFR0_EL1

- 只读系统寄存器,全称为 AArch64 Memory Model Feature Register 0。它提供了关于处理器内存模型和相关功能的详细信息,主要是描述与内存管理和虚拟化相关的特性。

- PARange (Physical Address Range, Bits [3:0])表示支持的物理地址大小:

- 0b0000: 32 位

- 0b0001: 36 位

- 0b0010: 40 位

- 0b0011: 42 位

- 0b0100: 44 位

- 0b0101: 48 位

- 0b0110: 52 位

- 其他值可能表示未来扩展。

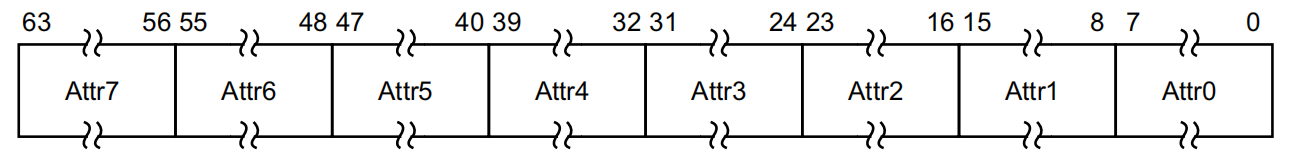

MAIR_EL2

https://blog.csdn.net/suifengershi2000/article/details/122805722

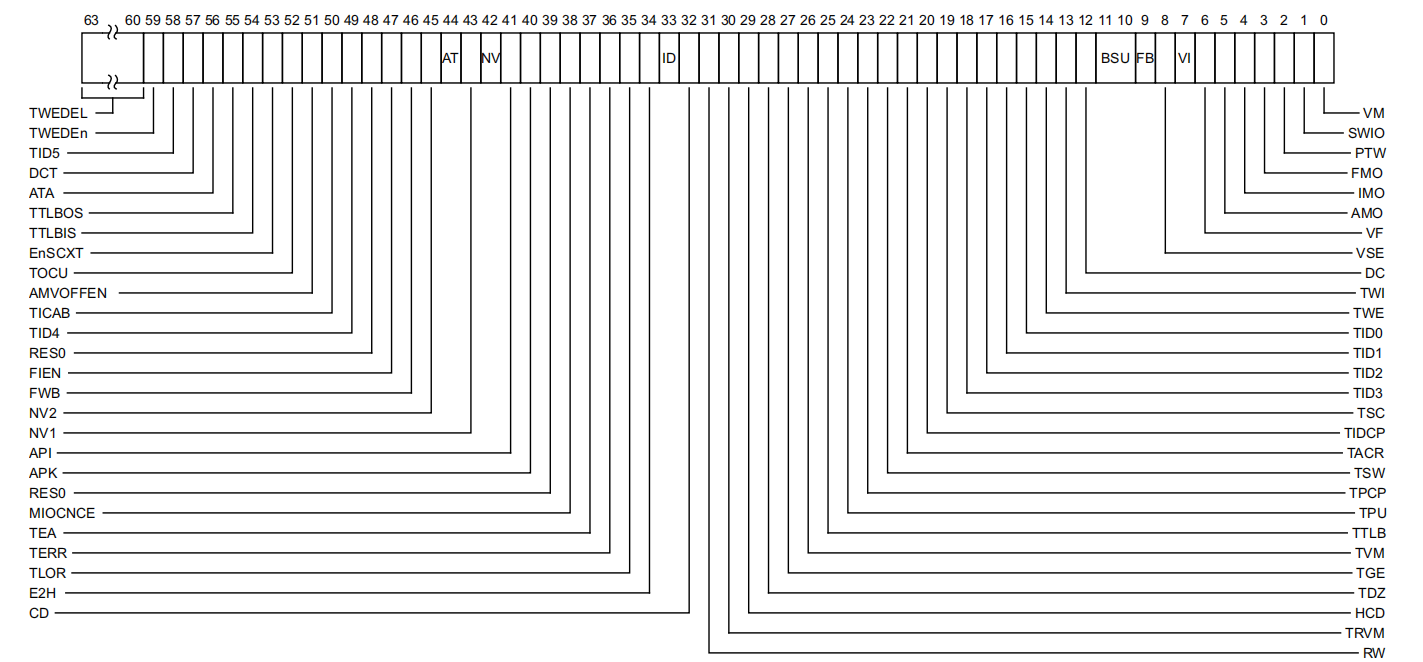

HCR_EL2

HCR_EL2(Hypervisor Configuration Register, EL2)是 ARMv8-A 架构中用于虚拟化环境的系统寄存器

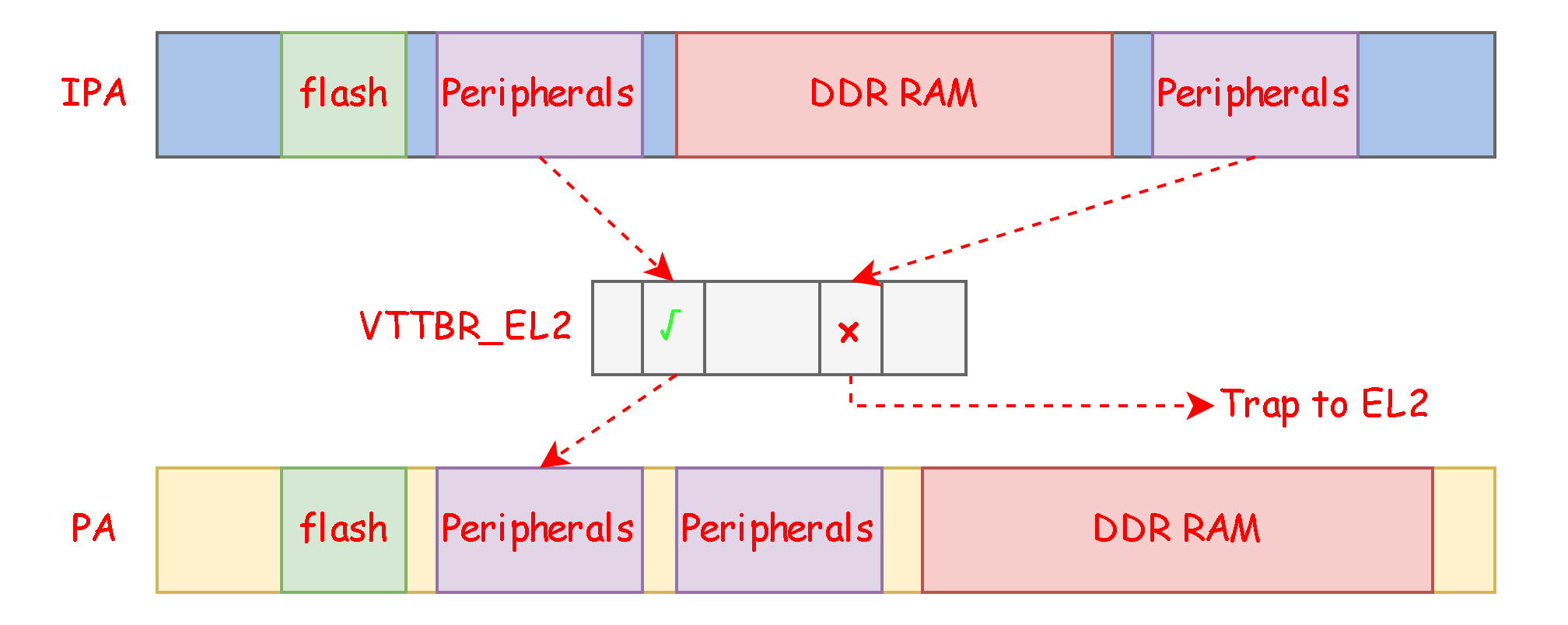

VM (Bit 0) - Virtual Memory:

- 作用:开启或关闭 Stage-2 地址转换。

- 0:虚拟机的内存访问直接使用 Stage-1 转换(不经过 Hypervisor 的额外检查)。

- 1:启用 Stage-2 转换,虚拟机的内存访问由 Hypervisor 控制(通过 VTTBR_EL2 和 VTCR_EL2)。

- 类比:就像给虚拟机的内存访问加了一道“安检门”,Hypervisor 可以检查和重新映射虚拟机的地址。

SWIO (Bit 1) - Set/Way Invalidation Override:

- 作用:控制虚拟机对缓存维护指令(如 DC ISW)的行为。

- 0:虚拟机的缓存维护指令按正常方式执行。

- 1:将虚拟机的缓存维护指令转换为 Hypervisor 的陷阱(trap),由 Hypervisor 处理。

- 类比:虚拟机想“清理房间”(缓存),Hypervisor 可以选择自己来做,而不是让虚拟机直接干。

PTW (Bit 2) - Protected Table Walk:

- 作用:保护 Stage-1 转换表遍历(table walk)时的内存访问。

- 1:如果 Stage-1 转换表遍历访问到设备内存,会触发异常到 Hypervisor。

- 类比:如果虚拟机在查“地址地图”时误入“危险区域”(设备内存),Hypervisor 会介入阻止。

AMO (Bit 5) - Asynchronous Abort Mask Override:

- 作用:控制异步异常(如 SError)是否路由到 Hypervisor。

- 1:异步异常会被捕获到 EL2,由 Hypervisor 处理。

- 类比:如果虚拟机遇到“突发事故”(异步异常),Hypervisor 会先接手处理,而不是让虚拟机自己解决。

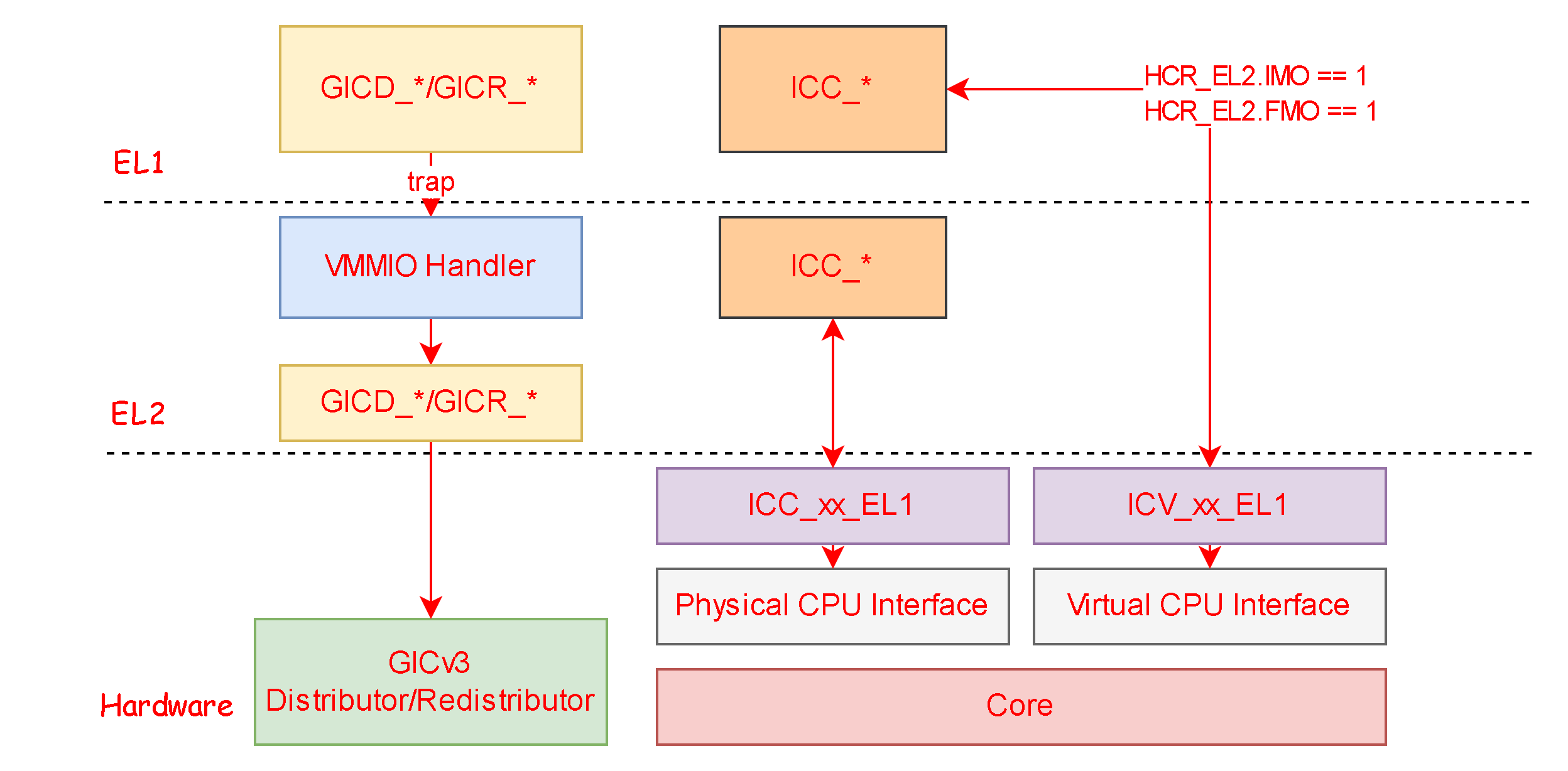

IMO (Bit 4) - IRQ Mask Override:

- 作用:控制物理中断(IRQ)是否路由到 Hypervisor。

- 1:物理中断会被捕获到 EL2。

- 类比:虚拟机收到“电话”(中断),Hypervisor 可以选择先接听。

FMO (Bit 3) - FIQ Mask Override:

- 作用:类似 IMO,但针对快速中断(FIQ)。

- 1:FIQ 会被路由到 EL2。

- 类比:类似 IRQ,但处理更紧急的“快递通知”。

TWI (Bit 13) - Trap Wait-for-Interrupt:

- 作用:控制虚拟机的 WFI(Wait For Interrupt)指令是否陷入 Hypervisor。

- 1:虚拟机的 WFI 指令会触发异常到 EL2。

- 类比:虚拟机想“睡觉”等待中断,Hypervisor 可以说:“先问问我!”

TSC (Bit 19) - Trap SMC:

- 作用:控制虚拟机的 SMC(Secure Monitor Call)指令是否陷入 Hypervisor。

- 1:SMC 指令会触发异常到 EL2,而不是进入 EL3(Secure Monitor)。

- 类比:虚拟机想“呼叫安全主管”(SMC),Hypervisor 可以拦截。

TIDCP (Bit 20) - Trap Implementation Defined Control:

- 作用:控制对某些实现定义寄存器的访问是否陷入 Hypervisor。

- 1:访问某些特定寄存器会触发异常到 EL2。

- 类比:虚拟机想动“特殊设备”,Hypervisor 会先检查。

RW (Bit 31) - Register Width:

- 作用:决定虚拟机的执行状态是 AArch64 还是 AArch32。

- 0:虚拟机运行在 AArch32 模式。

- 1:虚拟机运行在 AArch64 模式。

- 类比:决定虚拟机用“新款电脑”(64 位)还是“老款电脑”(32 位)运行。

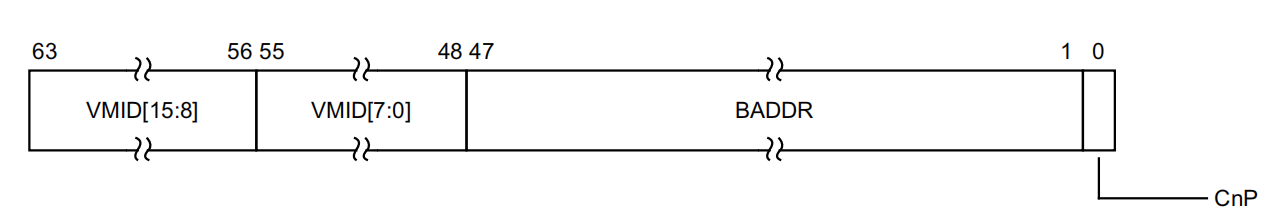

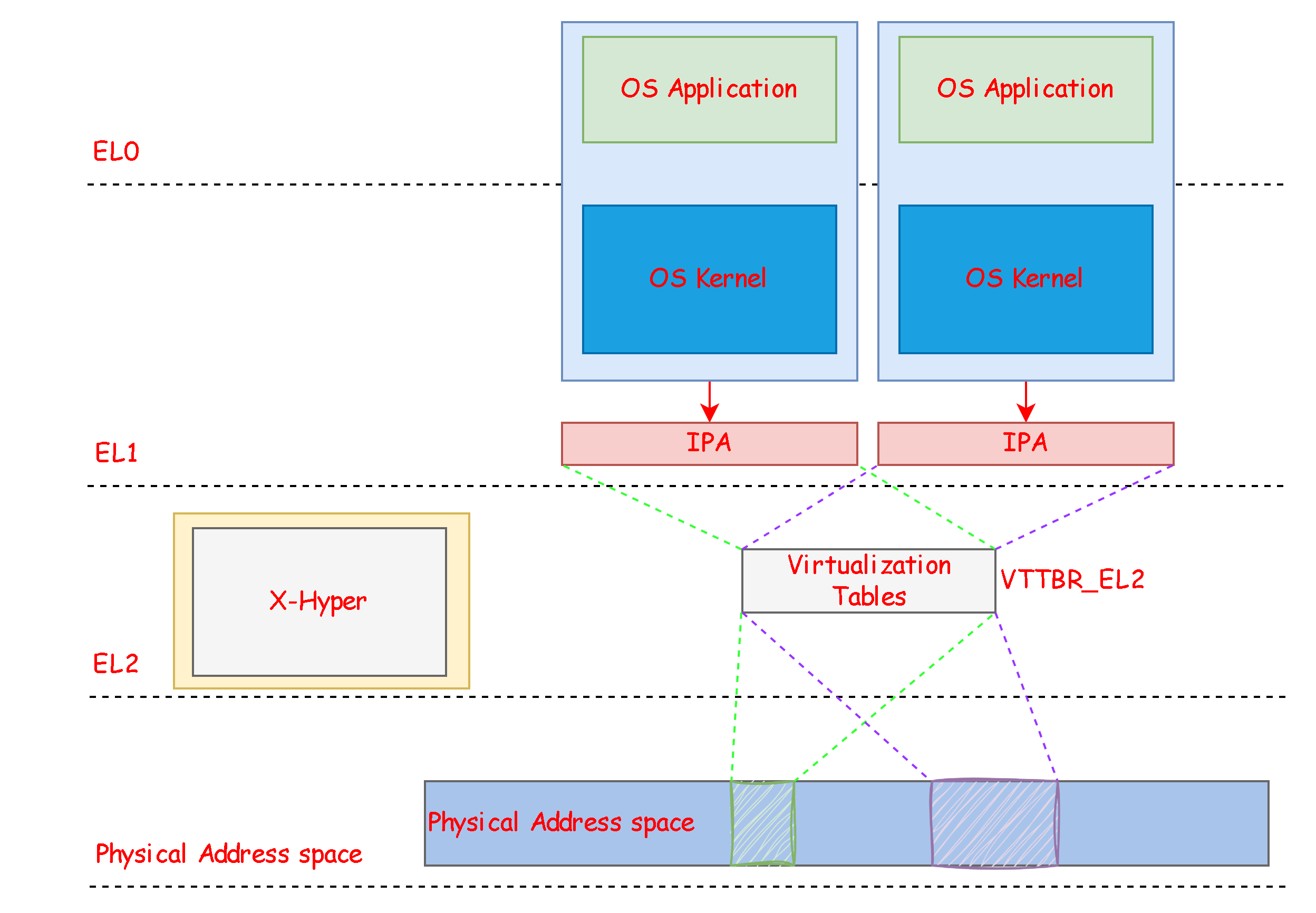

VTTBR_EL2

**BADDR [47:1]**(Base Address,Bits [47:1]):

- 存储 Stage-2 页面表(L0 表)的物理地址(Physical Address)。

- 地址必须按页面大小对齐(通常 4KB,即 Bits [11:0] 为 0)。

**VMID [63:48]**(Virtual Machine Identifier,Bits [63:48]):

- 虚拟机标识符,用于区分不同虚拟机的页面表。

- 支持 8 位或 16 位 VMID(由 VTCR_EL2.VS 控制)。

- 确保多个虚拟机的 Stage-2 转换互不干扰(例如,KVM 为每个虚拟机分配唯一的 VMID)。

**CnP [0]**(Common not Private,Bit 0):

- 控制页面表是否共享 TLB(Translation Lookaside Buffer)条目。

- 0:页面表为私有,仅用于当前虚拟机。

- 1:页面表可共享(较少见)。

- 通常设为 0,代码中未显式设置,默认为 0。

MPIDR_EL1

Multiprocessor Affinity Register

【ARMv8/v9 系统寄存器 5 – CPU ID 判断寄存器 MPIDR_EL1 使用详细介绍】-CSDN博客

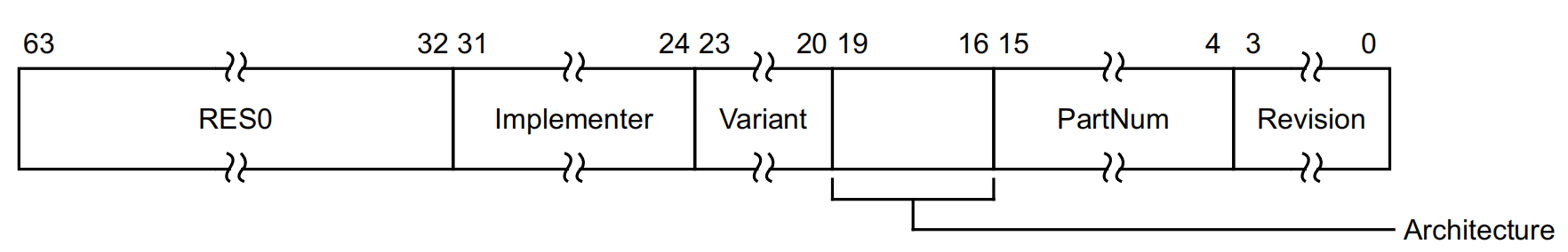

MIDR_EL1

| 位 | 字段名 | 描述 | 值(示例:0x410FD081) |

|---|---|---|---|

| [31:24] | Implementer | 实现者代码,表示 CPU 设计厂商。 | 0x41 = ARM Limited |

| [23:20] | Variant | 主要变体,区分同一部件号的不同版本。 | 0x0 = 变体 0 |

| [19:16] | Architecture | 架构版本,定义 CPU 的指令集架构。 | 0xF = ARMv8-A |

| [15:4] | PartNum | 部件号,标识具体 CPU 型号。 | 0xD08 = Cortex-A72 |

| [3:0] | Revision | 修订版,标识小版本更新。 | 0x1 = 修订版 1 |

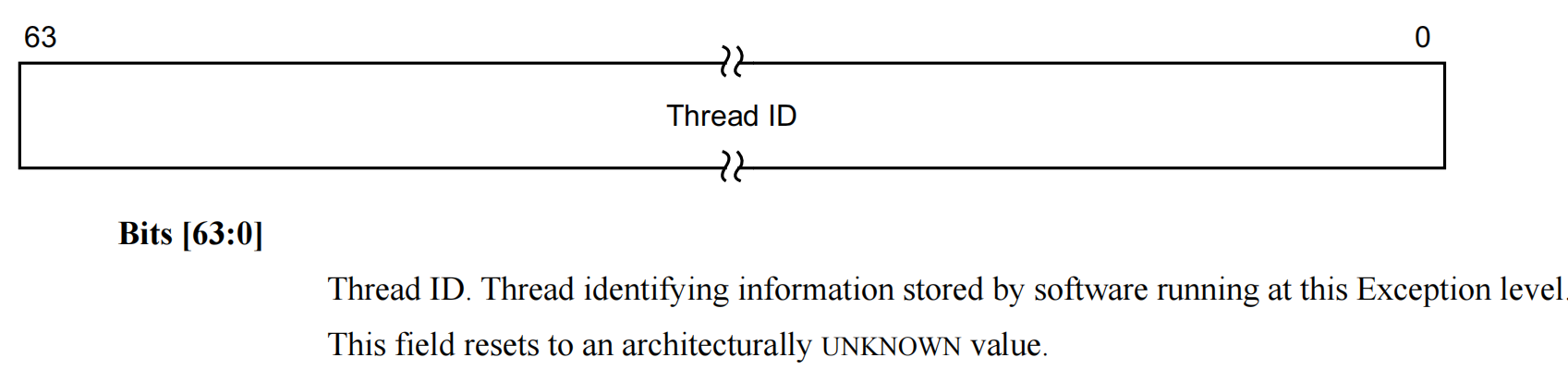

TPIDR_EL2

TPIDR_EL2 是 EL2(Hypervisor 模式)的专用系统寄存器,64 位宽,位于非安全世界(Non-Secure World)。

用途:

- 存储 Hypervisor 上下文相关的指针或标识符,通常用于:

- 线程标识:标识当前运行的 vCPU 或线程。

- 上下文切换:保存指向 Hypervisor 数据结构的指针(如 vCPU 结构体)。

- 快速访问:提供快速访问 Hypervisor 的全局或每线程数据。

- 操作系统或 Hypervisor 可以自由使用 TPIDR_EL2 存储任意数据(通常是一个指针),具体用途由软件定义。

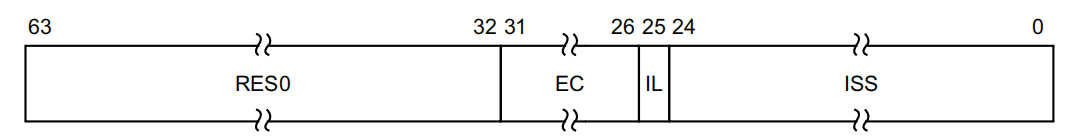

ESR_ELx

- ESR_ELx寄存器:当ARMv8处理器发生异常时,该寄存器记录异常原因信息,包括:

- EC(Exception Class)字段:高6位(bit[31:26]),表示异常类别。

- ISS(Instruction Specific Syndrome)字段:低26位,提供更详细的异常信息。

常见 EC 值(部分):

- 0x00: Unknown reason(未知原因)。

- 0x15: Trapped WFI/WFE 指令(由 HCR_EL2.TWI/TWE 触发)。

- 0x16:表示客户机执行的 HVC 指令触发了异常,且被陷阱到 EL2。

- 0x17: Trapped SMC 指令(由 HCR_TSC 触发)。

- 0x20: Instruction Abort from lower EL(指令页面错误,Stage-2)。

- 0x24: Data Abort from lower EL(数据页面错误,Stage-2)。

- 0x3C: Hypervisor Call(HVC 指令)。

- 该寄存器存在于多个异常级别,如ESR_EL1、ESR_EL2、ESR_EL3。

子字段:ISS被分为多个子字段,布局因EC而异。常见子字段包括:

- ISV **(bit[24])**:Instruction Syndrome Valid,表示ISS中的其他信息(如访问大小)是否有效(1:有效,0:无效)。

- SAS **(bit[23:22])**:Syndrome Access Size,访问大小(0:字节, 1:半字, 2:字, 3:双字)。

- **SSE (bit[21])**:Syndrome Sign Extend,符号扩展(1:符号扩展, 0:无)。

- **SRT (bit[20:16])**:Syndrome Register Transfer,涉及的寄存器编号(0-31)。

- SF **(bit[15])**:Sixty-Four bit register,寄存器宽度(1:64位, 0:32位)。

- AR **(bit[14])**:Acquire/Release semantics,获取/释放语义(1:有, 0:无)。

- **VNCR (bit[13])**:Virtual Nested Control Register相关(在嵌套虚拟化中用)。

- SET **(bit[12:11])**:Synchronous Error Type,同步错误类型。

- **FnV (bit[10])**:Fault not Valid,故障无效标志。

- **EA (bit[9])**:External Abort type,外部中止类型。

- CM **(bit[8])**:Cache Maintenance,缓存维护操作。

- **S1PTW (bit[7])**:Stage 1 Page Table Walk,是否为 Stage-1 页表遍历引起的错误。

- **WnR (bit[6])**:Write not Read,访问类型(1:写, 0:读)。

- **DFSC/IFSC (bit[5:0])**:Data/Instruction Fault Status Code,错误状态码(FSC),表示具体原因(如翻译错误、权限错误)。

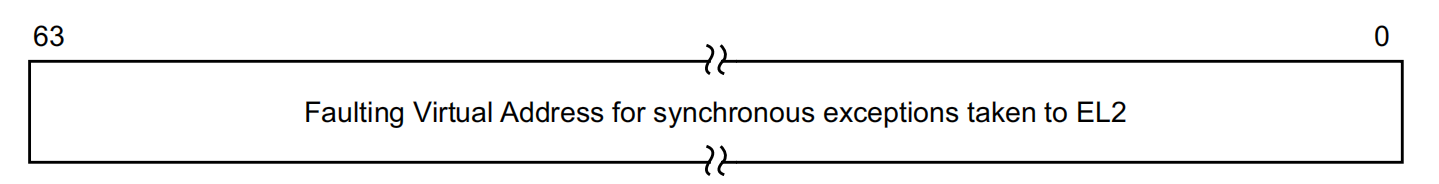

FAR_EL2

(Fault Address Register, Exception Level 2,故障地址寄存器),它记录触发内存访问异常的虚拟地址(VA)或中间物理地址(IPA)

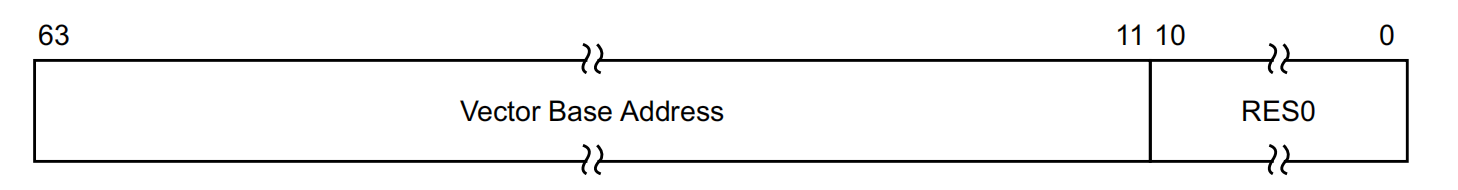

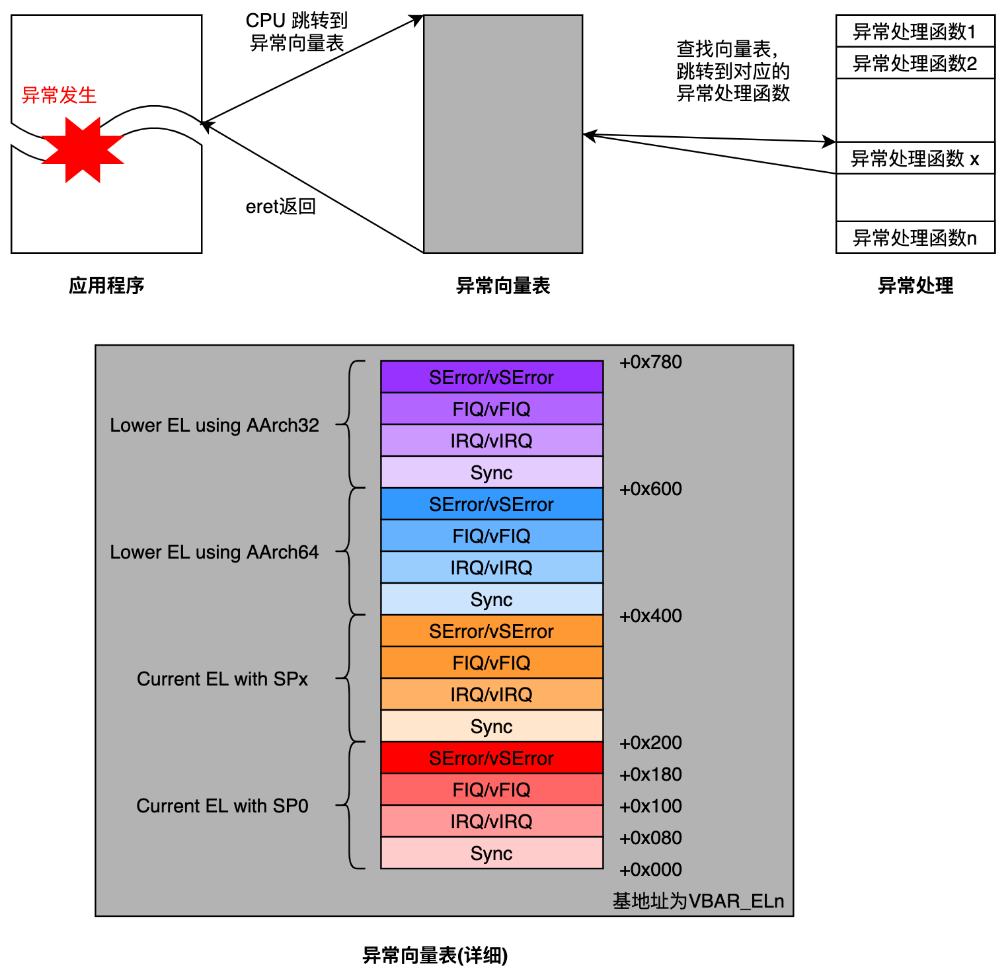

VBAR_ELx

https://zhuanlan.zhihu.com/p/578252899

异常向量表地址寄存器

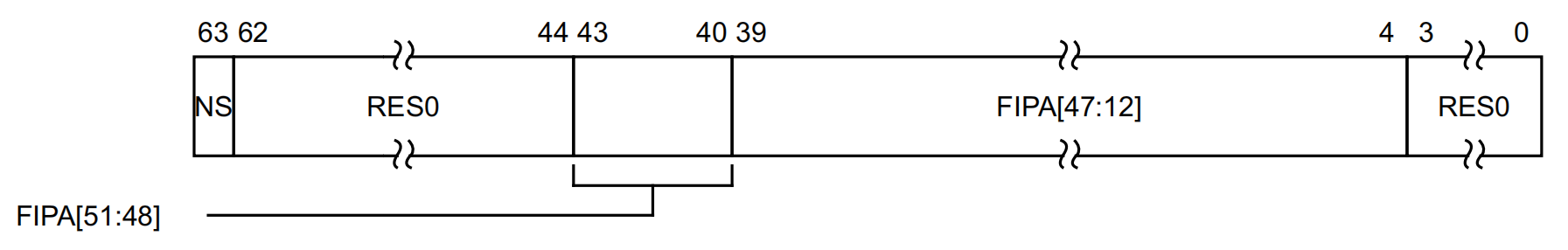

HPFAR_EL2

- 在 EL2 模式(Hypervisor 模式)下记录 Stage-2 地址转换过程中发生的页面错误(Page Fault)或权限错误的中间物理地址(Intermediate Physical Address, IPA)

- **Faulting IPA (bit[47:12])**:导致错误的 IPA,4KB 对齐。用HPFAR_EL2寄存器的bit[4,40]来存,bit[0,3]默认为0

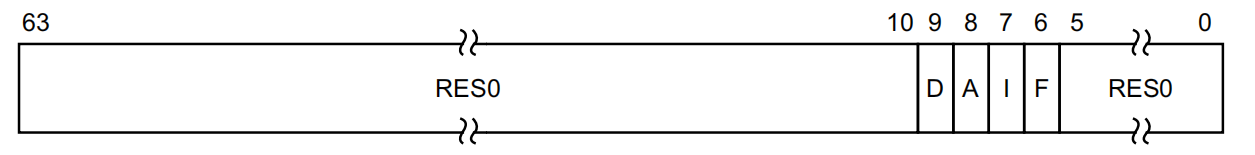

DAIF

DAIF 寄存器的全称是 Debug, Abort, IRQ, FIQ mask register(调试、异常终止、中断请求、快速中断请求屏蔽寄存器)。

- D(Debug):调试异常屏蔽位,用于屏蔽调试相关的异常(如断点、单步执行等)

- A(Abort):异常终止屏蔽位,用于屏蔽系统错误异常(如内存访问错误等)

- I(IRQ):中断请求屏蔽位,用于屏蔽普通中断(如外设中断)

- F(FIQ):快速中断请求屏蔽位,用于屏蔽快速中断(优先级高于 IRQ 的中断)

2.2 指令

MRS/MSR

MRS指令用于将程序状态寄存器的内容传送到通用寄存器中

MRS{条件} 通用寄存器,程序状态寄存器(CPSR或SPSR) |

MSR指令用于将操作数的内容传送到程序状态寄存器的特定域中

MSR{条件} 程序状态寄存器(CPSR或SPSR)_<域>,操作数 |

https://zhuanlan.zhihu.com/p/333926905

DMB、DSB、ISB

(1)Data Memory Barrier(DMB):数据内存屏障

主要用于多核处理器系统中,不同的处理器可能同时执行数据内存传输指令。DMB指令确保在DMB之前的所有显式数据内存传输指令都已经在内存中读取或写入完成,同时确保任何后续的数据内存传输指令都将在DMB执行之后开始执行,否则有些数据传输指令可能会提前执行。

(2)Data Synchronization Barrier(DSB):数据同步屏障

在计算机的体系结构中,处理器在执行指令时通常会利用指令流水线来提高性能。但也会产生一些问题,比如在多线程编程中,两个线程同时对共享的内存进行读写操作,由于读/写操作的重排序,就会导致数据的不一致。

当执行DSB指令时,它确保在DSB之前的所有显式数据内存传输指令都已经在内存中读取或写入完成,同时确保任何后续的指令都将在DSB执行之后开始执行。

DSB 接受不同的选项,控制同步的范围:

- sy(System):最强的同步,确保所有处理器核和设备完成内存操作。

- ish(Inner Shareable):同步内部可共享域(通常是同一集群的核)。

- ishst 确保内部可共享域(同一集群的核)内的所有写操作(store)完成。

- nsh(Non-Shareable):仅同步本地核的内存操作。

- osh(Outer Shareable):同步外部可共享域(跨集群或设备)。

(3)Instruction Synchronization Barrier(ISB):指令同步屏障

指令的流水线允许处理器同时执行多条指令的不同阶段,然而这样并行执行可能会导致一些问题,特别是涉及到上下文切换的情况,如实时操作系统的任务切换。当上下文切换时,可能指令流水线中的指令还在执行,而此时上下文已经改变,导致指令执行的结果不正确。

通过插入ISB指令,处理器会将流水线中的指令全部刷新,从而确保之前的指令不会影响后续指令的执行,并且后续指令将从正确的上下文开始重新获取。

https://blog.csdn.net/tilblackout/article/details/131949061

MPIDR_EL1

U, bit [30]:0表示多核处理, 1表示单核处理

MT, bit [24]:0表示没有使用单核超线程, 1表示使用了单核超线程。

不支持超线程的cpu, Aff0表示核id。每个core上都有一个这个寄存器

https://blog.csdn.net/sinat_32960911/article/details/138754997

https://zhuanlan.zhihu.com/p/656806517

LDXR/STXR

LDXR是独占内存加载指令,它以独占的方式加载内存地址的值到通用寄存器。

STXR是独占内存存储指令,它以独占的方式将通用寄存器中的值存储到内存地址。执行的结果放在 ws 寄存器中,如果该寄存器为0则执行成功。

LDXR和STXR指令必须配对使用,位于这两条指令之间的代码是原子的。

当 CPU 通过LDXR指令从内存加载数据时,CPU 会把这个内存地址标记为独占访问,然后 CPU 内部的独占监视器的状态就变为独占访问状态。当执行到STXR指令时,需要根据独占监视器的状态来做决定:

- 如果是独占访问状态并且

STXR指令要存储的地址正好是刚才标记过的地址,那么STXR指令执行成功,返回0,并且独占监视器的状态变为开放访问状态。 - 如果是开放访问状态,那么

STXR指令执行失败,返回1,并且独占监视器的状态仍然保持开放访问状态。

https://tomsjtu.github.io/notes/arm/atomic/

STR/LDR/MOV

STR: STR是将寄存器中的数字载入内存

LDR:用于将内存中的数据存入寄存器中;

MOV:在ARM体系中,mov只能用于数据在寄存器之间的移动或者往寄存器中写入立即数

https://blog.csdn.net/horizontalview/article/details/50773740

LDP/STP

LDR:从指定的地址加载两个通用寄存器的值

STP:将两个通用寄存器的值存储到指定地址

https://blog.csdn.net/sinat_32960911/article/details/131533128

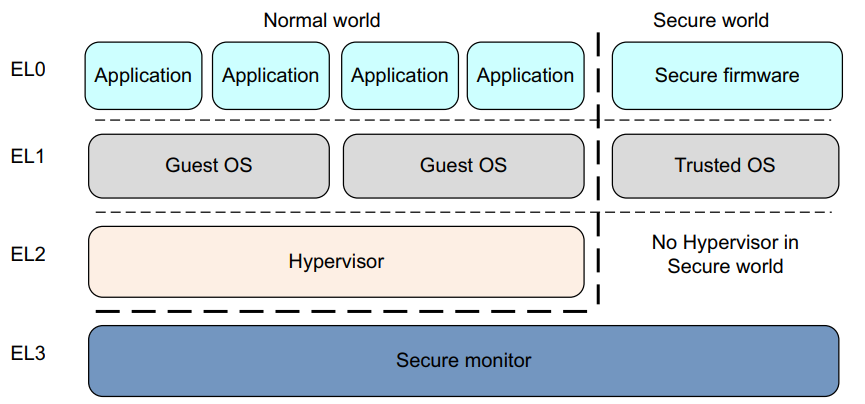

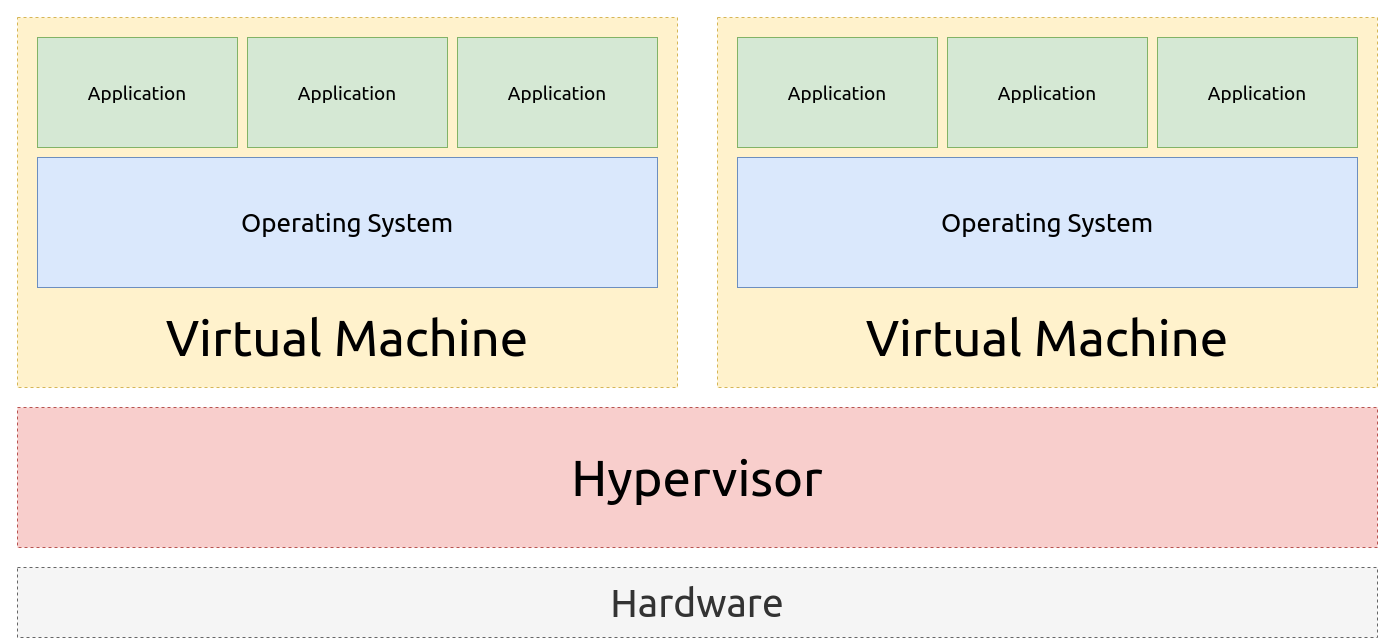

2.3 异常

- EL0:用户特权,运行普通用户程序

- EL1:系统特权,运行操作系统内核

- EL2:运行虚拟机监视器

- EL3:运行安全监控器

minos 2.1 中断虚拟化——ARMv8 异常处理 - Rand_CS - 博客园

https://zhuanlan.zhihu.com/p/578252899

异常向量表。向量可以分为两大类,四种:

- Exception from Lower EL,从低特权级来的异常

- 低特权级的执行状态为 AArch64

- 低特权级的执行状态为 AArch32

- Exception from the current EL,异常就来自当前特权级

- 当前选择了使用 SP_EL0 处理异常,就是处理异常使用 EL0 的栈空间

- 当前选择了使用 SP_ELx 处理异常,异常处理使用当前特权级的栈空间

2.4 内存管理

https://blog.csdn.net/flyingnosky/category_11603998.html

https://armv8-doc.readthedocs.io/en/latest/12.html

https://developer.arm.com/documentation/102142/0100

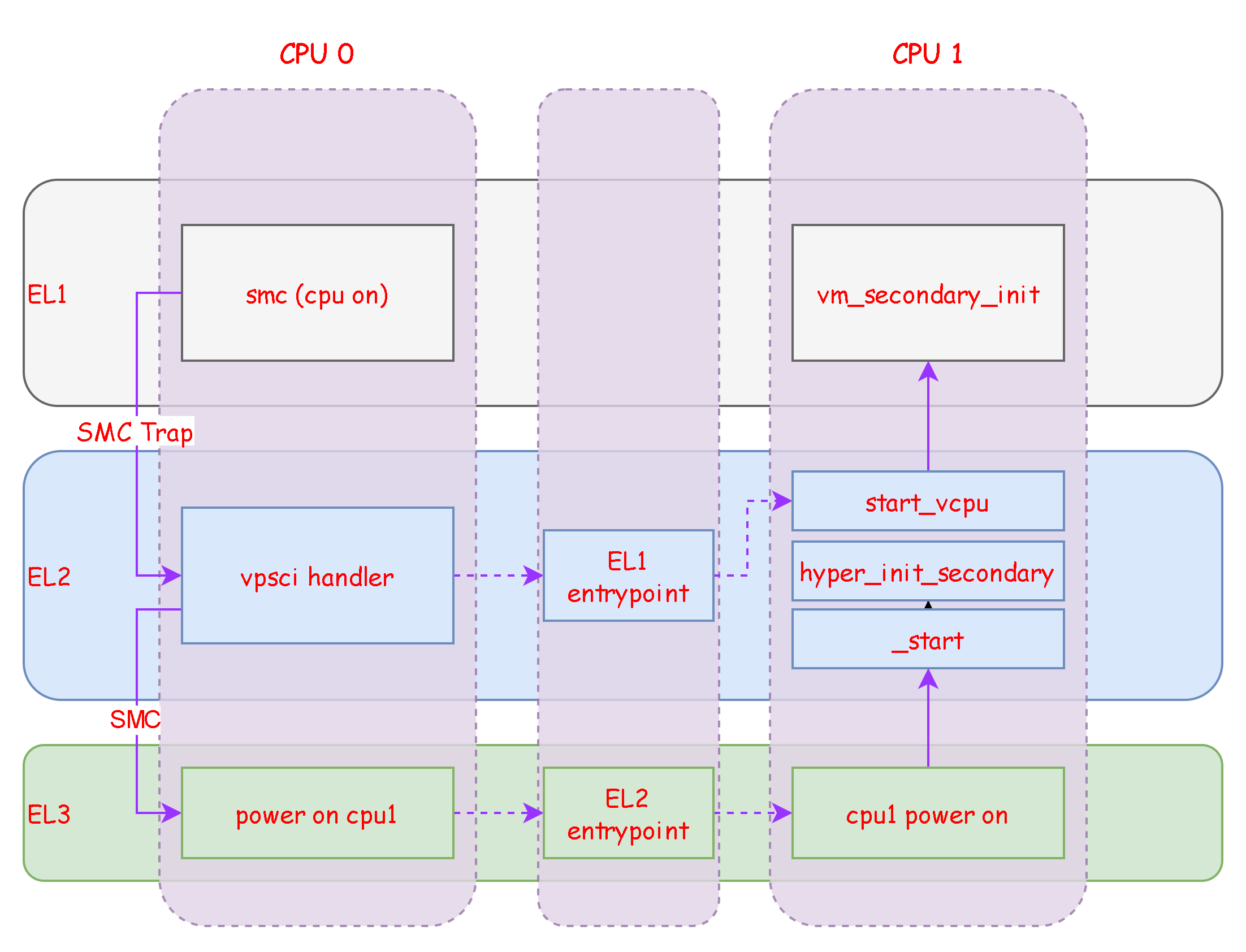

2.5 PSCI

Power State Coordination Interface(电源状态协调接口)。

作用:

- 提供标准化的 API,允许操作系统(OS)或 Hypervisor 管理 CPU 的电源状态和多核协调。

- 通过 SMC(Secure Monitor Call,安全监控调用)或 HVC(Hypervisor Call,虚拟化调用)与 Secure Monitor(EL3)或 Hypervisor(EL2)交互。

以下是 PSCI 的常见函数(基于 ARM PSCI 1.0 规范):

| 函数 | ID(SMC/HVC) | 功能 | 参数 |

|---|---|---|---|

| PSCI_VERSION | 0x84000000 | 返回 PSCI 版本 | 无 |

| CPU_ON | 0xC4000003 | 启动指定 CPU | 目标 CPU ID,入口地址,上下文 ID |

| CPU_OFF | 0x84000002 | 关闭当前 CPU | 无 |

| CPU_SUSPEND | 0xC4000001 | 挂起 CPU 到低功耗状态 | 电源状态,入口地址,上下文 ID |

| SYSTEM_OFF | 0x84000008 | 关闭整个系统 | 无 |

| SYSTEM_RESET | 0x84000009 | 重启整个系统 | 无 |

2.6 GICV3

https://zhuanlan.zhihu.com/p/261379308

官方文档:GICv3 and GICv4 Software Overview

IRQ****(普通中断请求):

- IRQ 是 ARM 架构中用于处理常规中断的机制,适用于大多数外部设备(如定时器、UART、磁盘控制器)或内部事件(如异常、错误)。

- 优先级较低,适合需要灵活处理、可能涉及上下文切换的场景。

- 由 GIC(Generic Interrupt Controller,通用中断控制器)分发,触发到目标异常级别(如 EL1 或 EL2)。

FIQ****(快中断请求):

- FIQ 是 ARM 架构中专为高优先级、时间敏感的中断设计的机制,旨在实现快速响应和低延迟处理。

- 优先级高于 IRQ,适合实时性要求高的场景(如高性能设备或关键系统事件)。

- 通常由 GIC 分发,且在某些实现中可能有专用的 FIQ 通道。

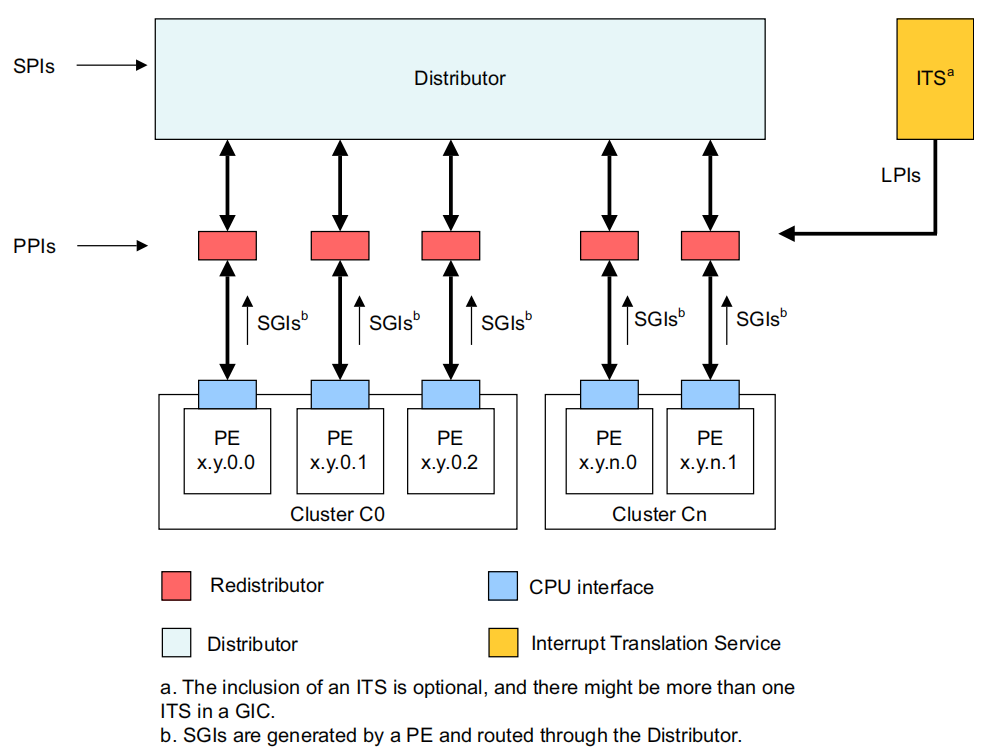

2.6.1 GIC-V3架构

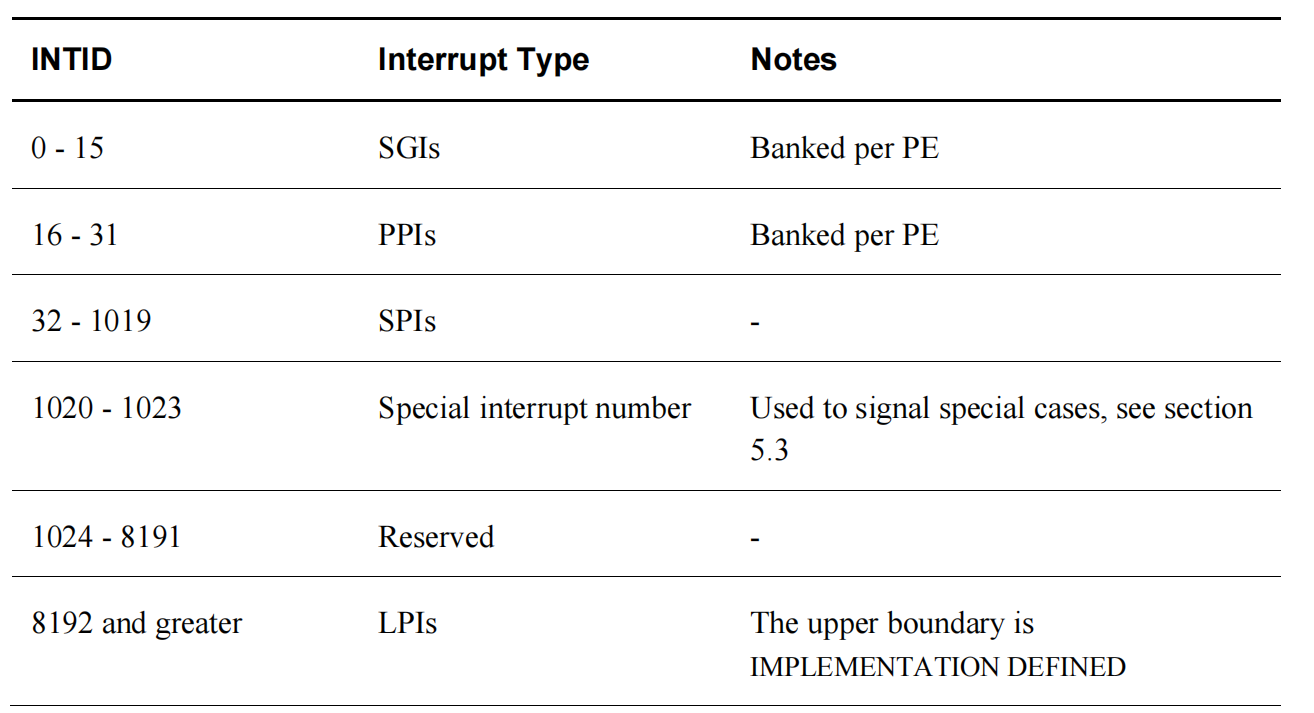

四种中断类型:

SPI(Shared Peripheral Interrupt****,共享外设中断):

- 来源:外设硬件(如 UART、定时器、磁盘控制器),通常由多个 CPU 核心共享。

- 用途:处理来自外部设备的通用中断。

- 分发:通过 GIC 分发器(Distributor)分发到任意或指定 CPU 核心(由 GICD 配置决定)。

- 触发方式:电平触发(Level-sensitive)或边沿触发(Edge-triggered)。

PPI(Private Peripheral Interrupt****,私有外设中断):

- 来源:与特定 CPU 核心关联的外设(如每个核心的私有定时器或 PMU)。

- 用途:处理特定 CPU 核心的私有中断。

- 分发:仅分发到关联的 CPU 核心,无法共享。

- 触发方式:通常是电平触发或边沿触发,具体由设备决定。

SGI(Software Generated Interrupt****,软件生成中断):

- 来源:软件触发,通常由一个 CPU 核心通过写入 GIC 寄存器(如 GICD_SGIR)生成,发送到其他核心。

- 用途:核间通信(Inter-Processor Interrupt, IPI),如调度、同步或虚拟化消息传递。

- 分发:由软件指定目标 CPU(单核、组播或广播)。

- 触发方式:通常是边沿触发。

LPI(Locality-specific Peripheral Interrupt****,局部外设中断):

- 来源:虚拟化环境中的虚拟设备或 ITS(Interrupt Translation Service,中断翻译服务)管理的设备。

- 用途:支持大规模虚拟化(如虚拟机或容器),与虚拟设备关联。

- 分发:通过 ITS 动态映射到虚拟机或 CPU,存储在 LPI 表中(由 Redistributor 和 ITS 管理)。

- 触发方式:通常是边沿触发,依赖 ITS 配置。

中断号:

2.6.2 GIC-V3 编程模型

GIC可被分为几个不同的组件,且每个组件都会支持一个或多个编程接口,这些接口又可分为内存映射型寄存器接口和系统寄存器接口两类。其中Distributor、Redistributor和ITS为内存映射型寄存器接口,而CPU interface则是系统寄存器接口。

- Distributor的寄存器映射地址:12.8章节。 GICD_*

- Redistributor 寄存器映射地址 12.10章节 GICR_*,每个cpu都有各自一套

- CPU interface 寄存器映射地址 12.12章节 ICC_*,每个cpu都有各自一套

2.6.2 中断分组

- Group0:Group0 中断是为 EL3(Exception Level 3)处理而设计的,通常被视为安全中断。在支持两种安全状态(安全和非安全)的系统中,Group0 始终是安全的,只有 EL3 可以处理这些中断。所有的 Group0 中断都被配置为 FIQ(Fast Interrupt Request),这意味着它们具有较高的优先级和快速处理的特性。

- Group1:Group1 中断进一步分为安全 Group1 和非安全 Group1。安全 Group1 中断由安全 EL1 处理,非安全 Group1 中断则由非安全的 EL1 或 EL2 处理。Group1 中断可以是 IRQ(Interrupt Request)或 FIQ,具体取决于当前的安全状态和处理器的异常级别。例如,当 Group1 的安全状态与 CPU 所处的当前异常级别的安全状态不同时,它为 FIQ,否则为 IRQ

SGI/PPI 分组配置:

- SGI(中断 ID 0~15):软件间通信中断(如 CPU 核心间唤醒),若需在非安全态使用(如 Linux 内核跨核 IPI),需将对应位设为 1(Group 1);

- PPI(中断 ID 16~31):CPU 私有外设中断(如每个核心独立的定时器中断),若定时器为非安全功能(如 Linux 系统定时器),则将对应位设为 1(Group 1);若为安全定时器(如安全监控),则设为 0(Group 0)。

2.6.3 Distributor寄存器

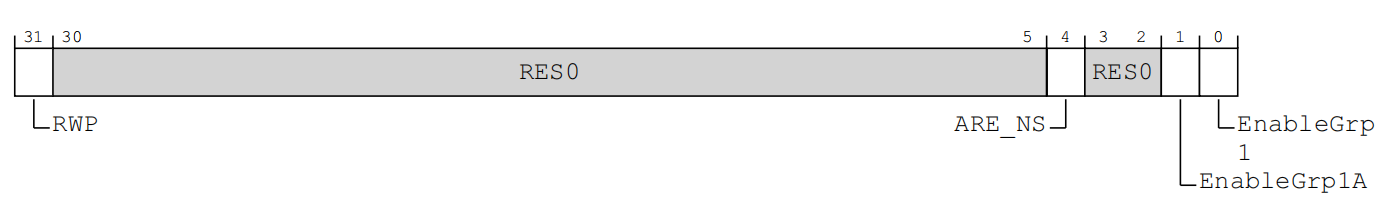

GICD_CTLR

安全模式下

- bit[0],EnableGrp0:用于使能 Group0 中断。当该位被设置时,Group0 中断将被允许通过分发器进行分发。

- bit[1],EnableGrp1NS:使能非安全 Group1 中断。在非安全状态下,设置此位可允许非安全 Group1 中断的分发

- bit[2],EnableGrp1S:使能安全 Group1 中断。如果系统支持安全状态,设置该位可允许安全 Group1 中断的分发。

- bit[4],安全状态下的亲和性路由使能位

- bit[6],DS:如果设置为 1,禁用安全状态,所有中断被视为非安全中断;如果设置为 0,启用安全状态,使得安全中断和非安全中断能够被分别处理。

- bit[31],REW:BIT_31 是等待回应位,当配置对应寄存器并写入到硬件后,可读取这个位来看是否已经写入配置信息并生效。

非安全模式下

- bit[0],使能非安全 Group1 中断

- bit[1],使能 Group 1 中断的 “活跃状态传播” 功能

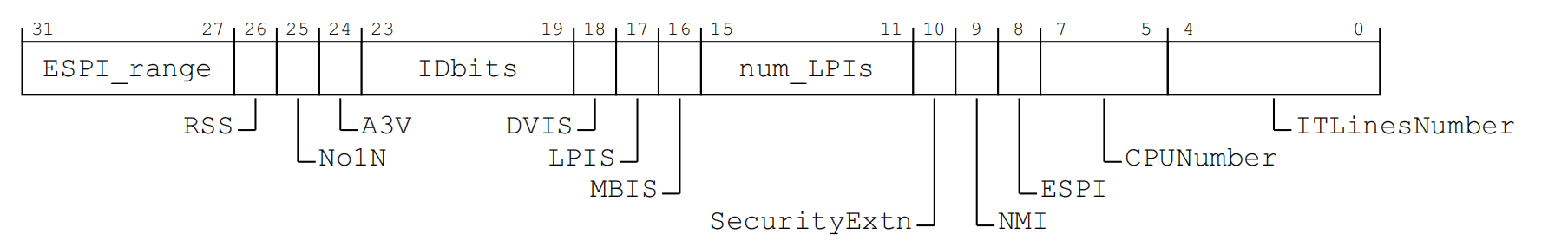

GICD_TYPER

中断类型控制器

[【ARMv8/v9 GIC 系列 3 – GIC 的 类型寄存器 GICD_TYPER】_gicd寄存器-CSDN博客](https://blog.csdn.net/sinat_32960911/article/details/139841966#:~:text=GICD_TYPER寄存器,即中断控制器类型寄存器,是ARM GIC(通用中断控制器)中的一个关键寄存器,它提供了关于GIC本身特性的详细信息。 以下是 GICD_TYPER 寄存器的各个字段的详细介绍: 这些位指示支持的扩展SPI(共享外设中断)的范围。,这对于支持大量外设中断的实现特别重要,最大可以支持范围是 (32*(ESPI_range %2B 1) %2B 4095)。)

- ITLinesNumber,bit[4:0],对于INTID范围为32到1019的情况,指示支持的最大SPI。如果这个字段的值为n,则最大SPI INTID为32*(n+1)减1。

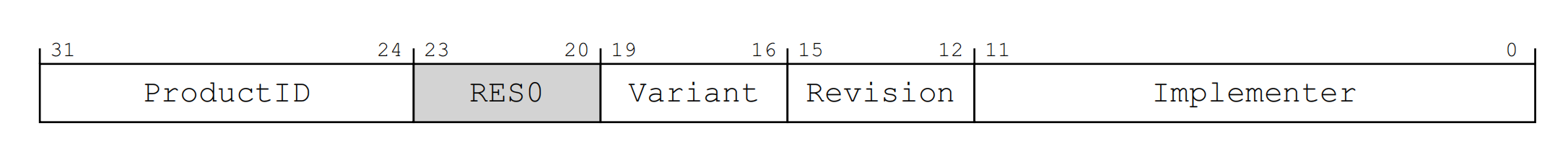

GICD_IIDR

GICD_IIDR 寄存器(Distributor Identification Register Register)是一个只读寄存器,主要用于标识中断分发器(Distributor)的硬件版本、实现厂商及功能特性

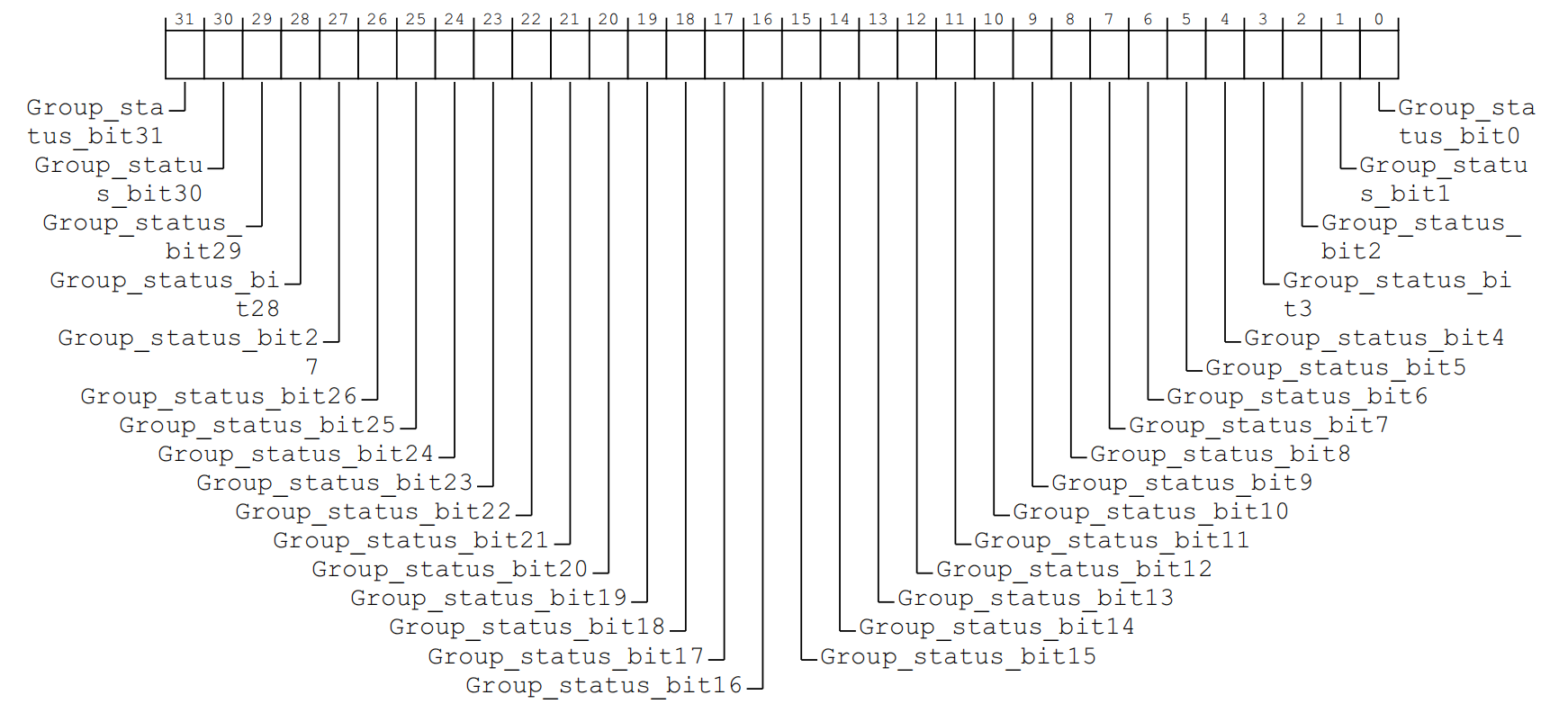

GICD_IGROUPR

此寄存器用于控制中断位于哪个group,一个bit位对应一个中断

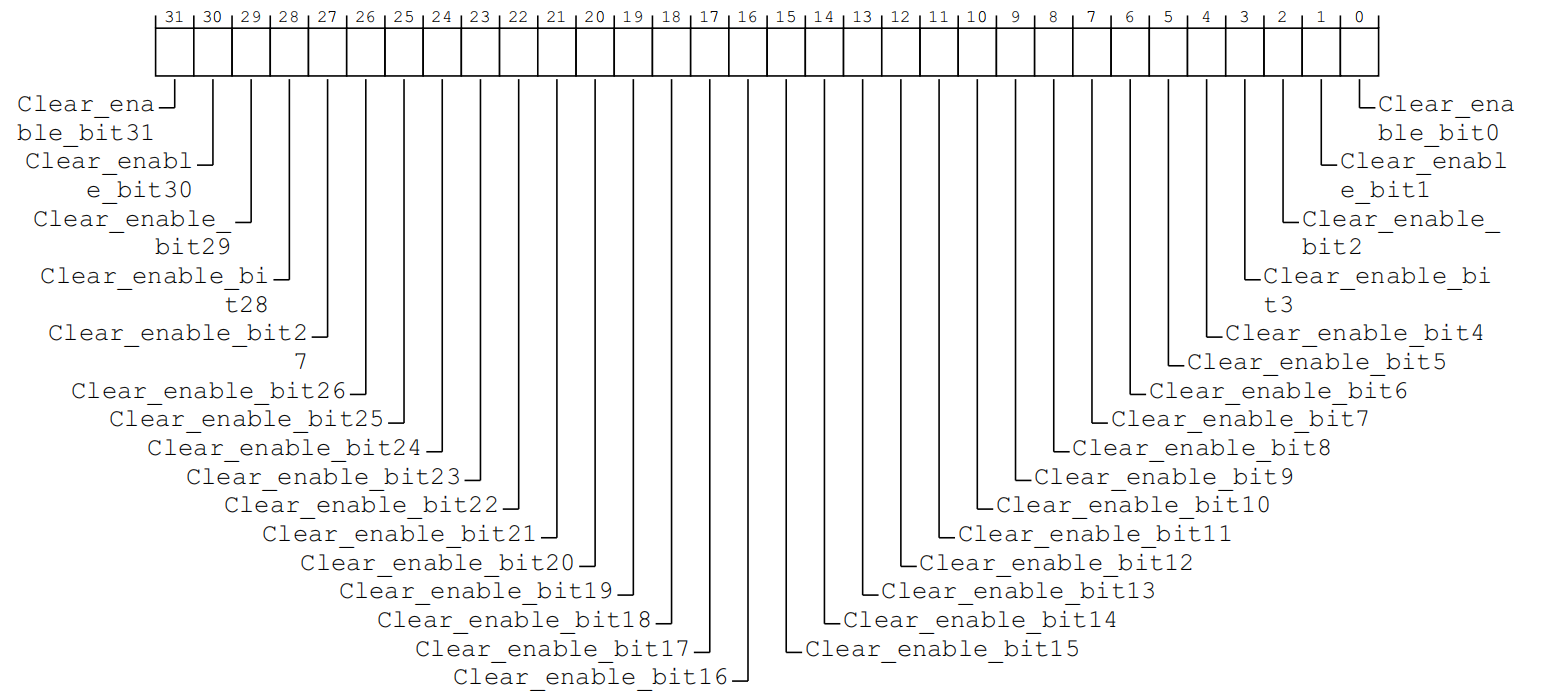

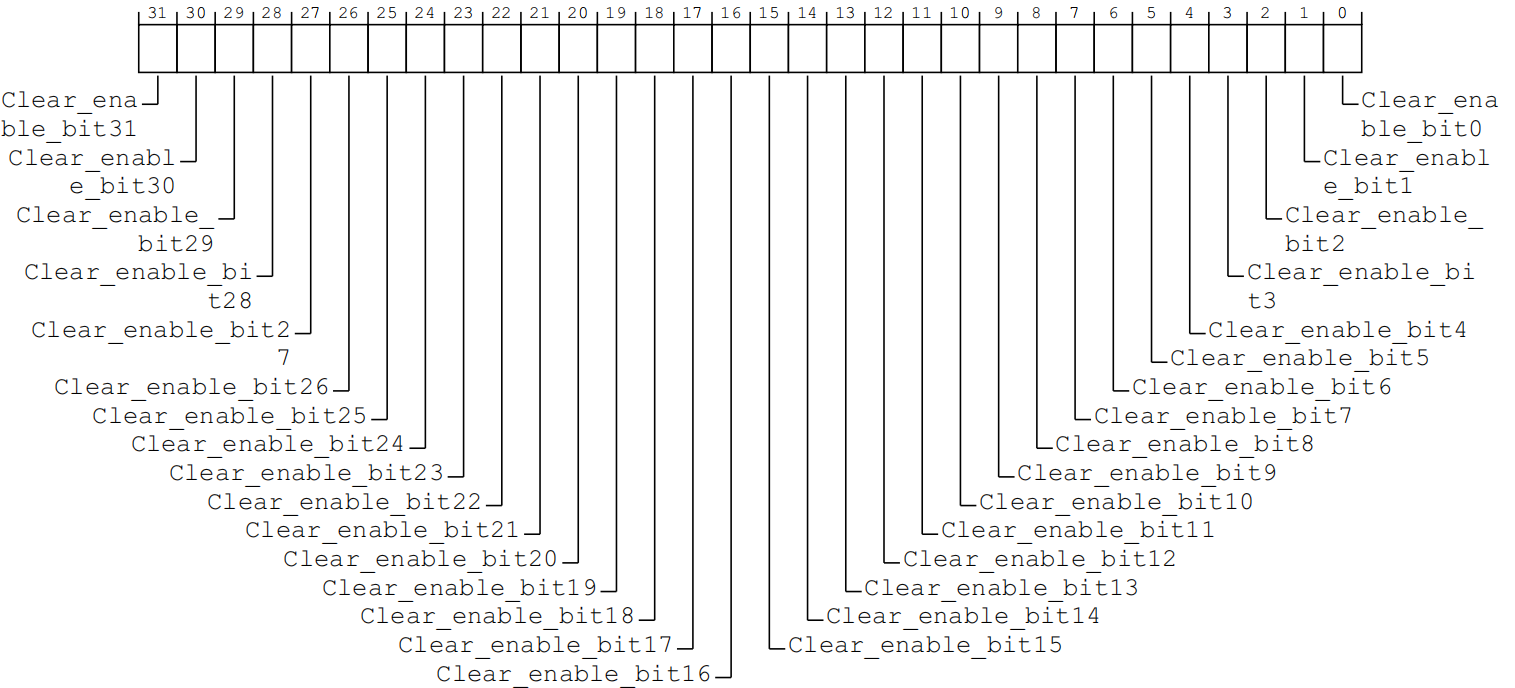

GICD_ICENABLER

中断禁用寄存器,只要在 ICENABLER 中对某 bit 写 1,就会把该中断的“Enable”状态清 0,等效于 禁用此中断。

每个寄存器 32-bit,一共覆盖 32 个中断 ID。<n> 的范围:

- n = 0 → 中断 ID 0–31

- n = 1 → ID 32–63

- …以此类推

计算公式: Interrupt ID = 32 * n + bit_position

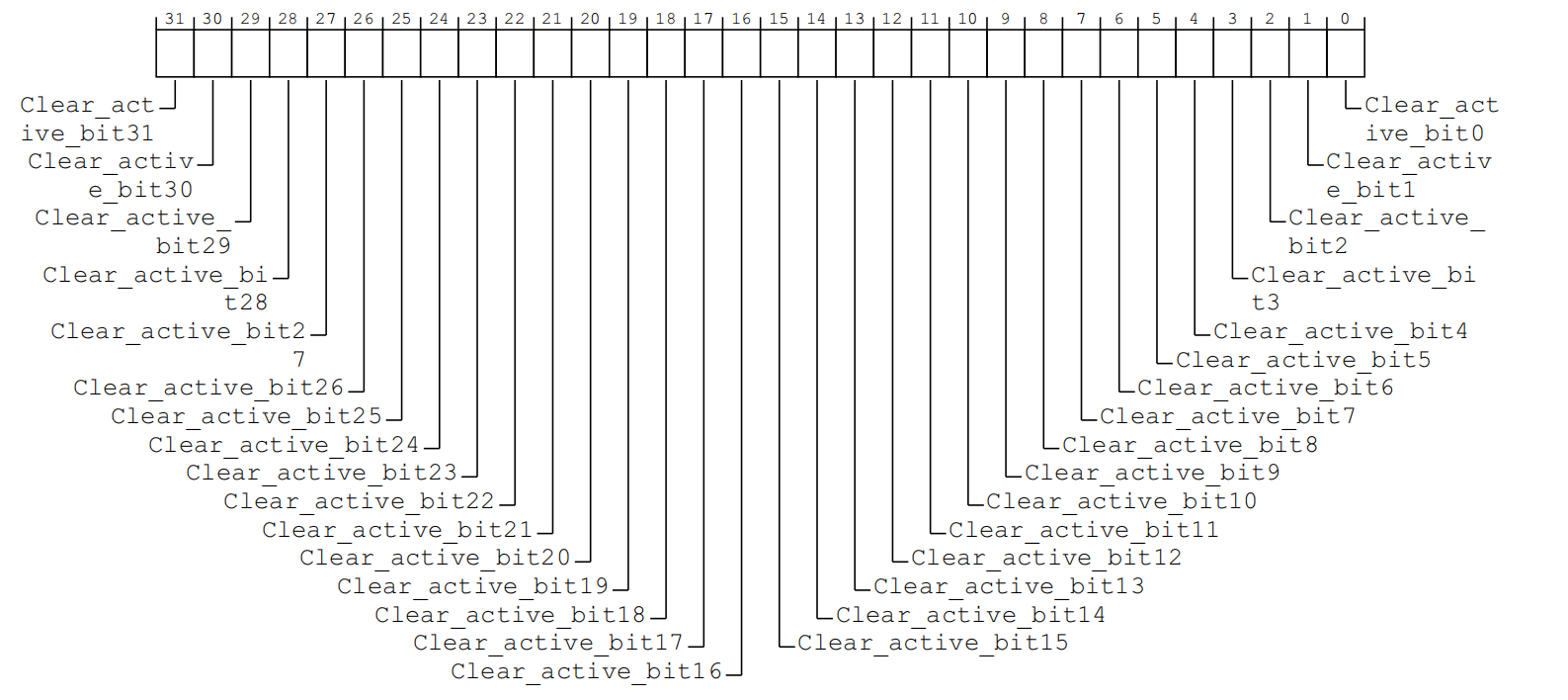

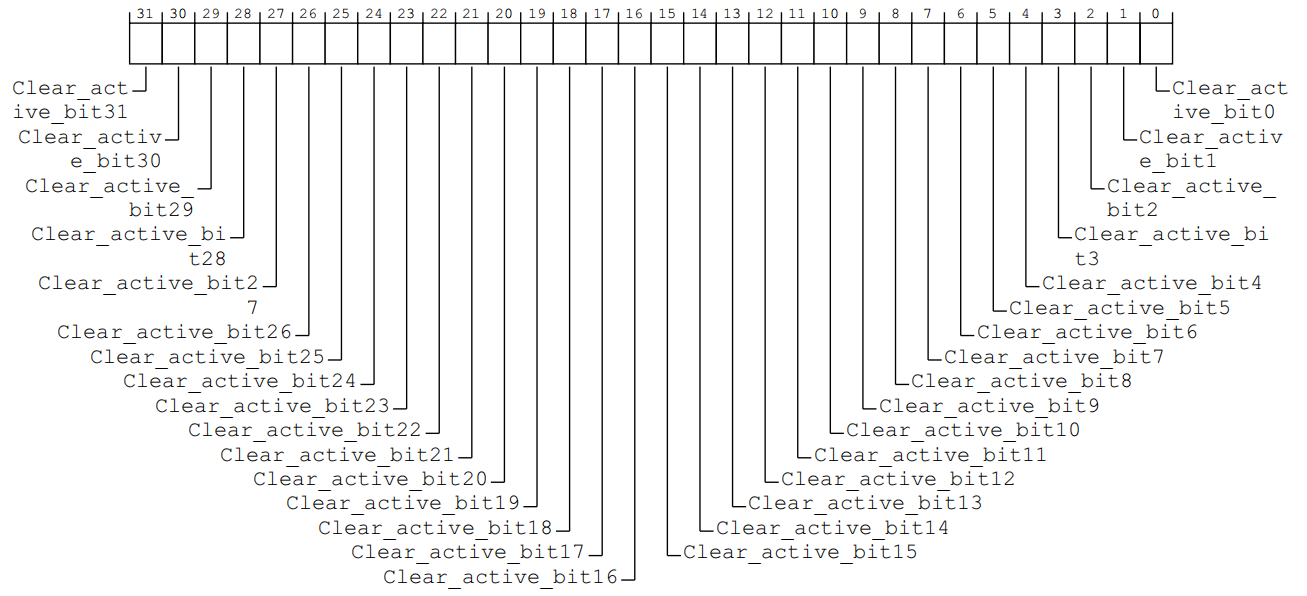

GICD_ICACTIVER

清除活跃**状态寄存器

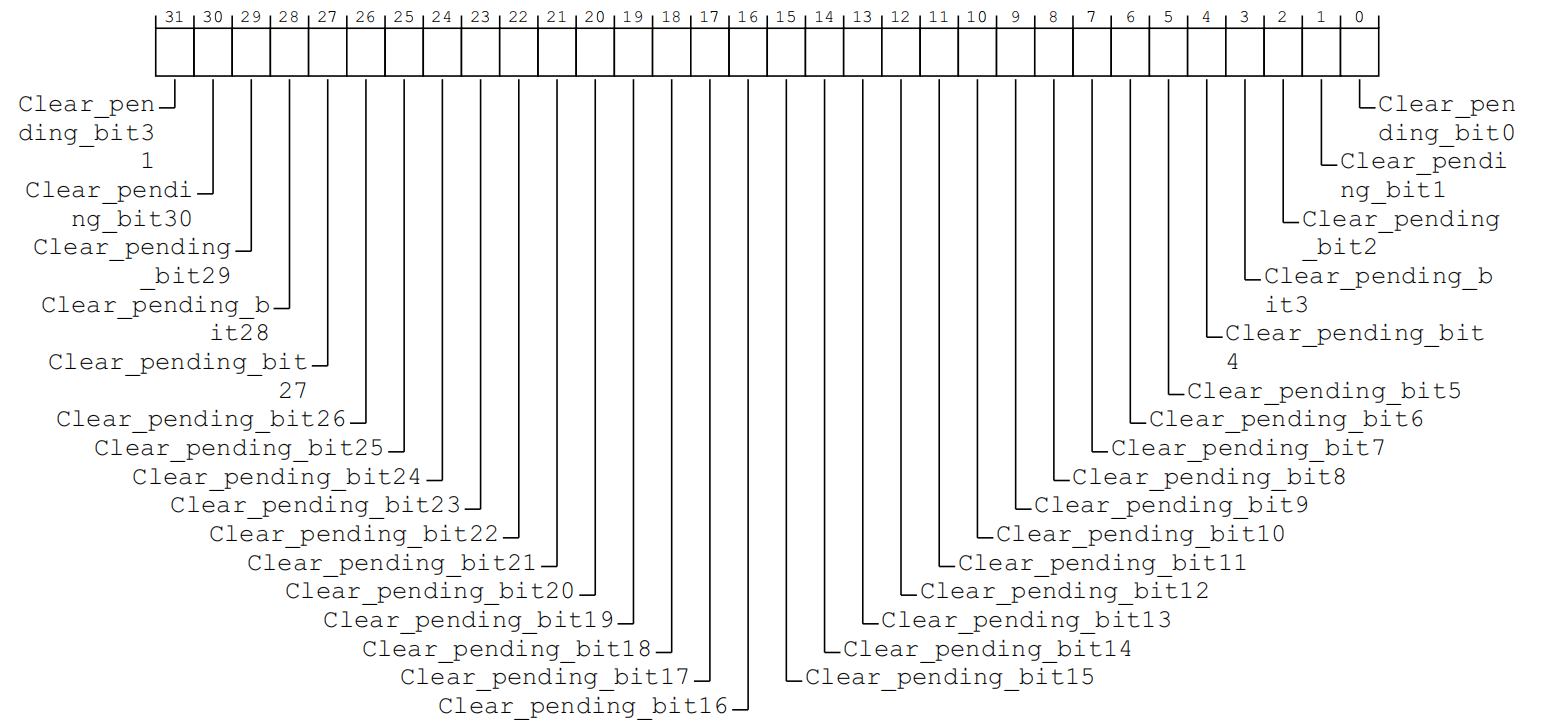

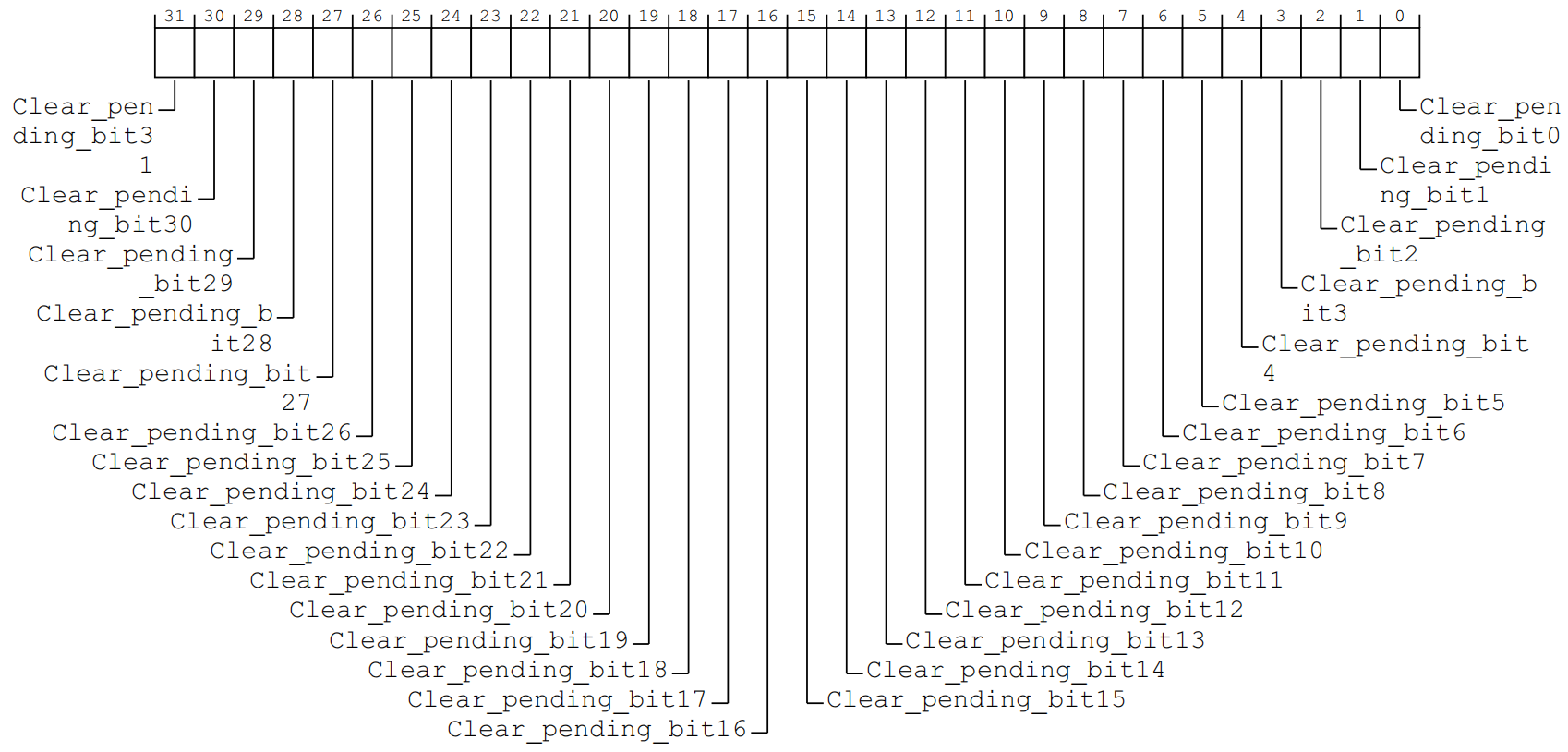

GICD_ICPENDR

清除挂起**状态寄存器

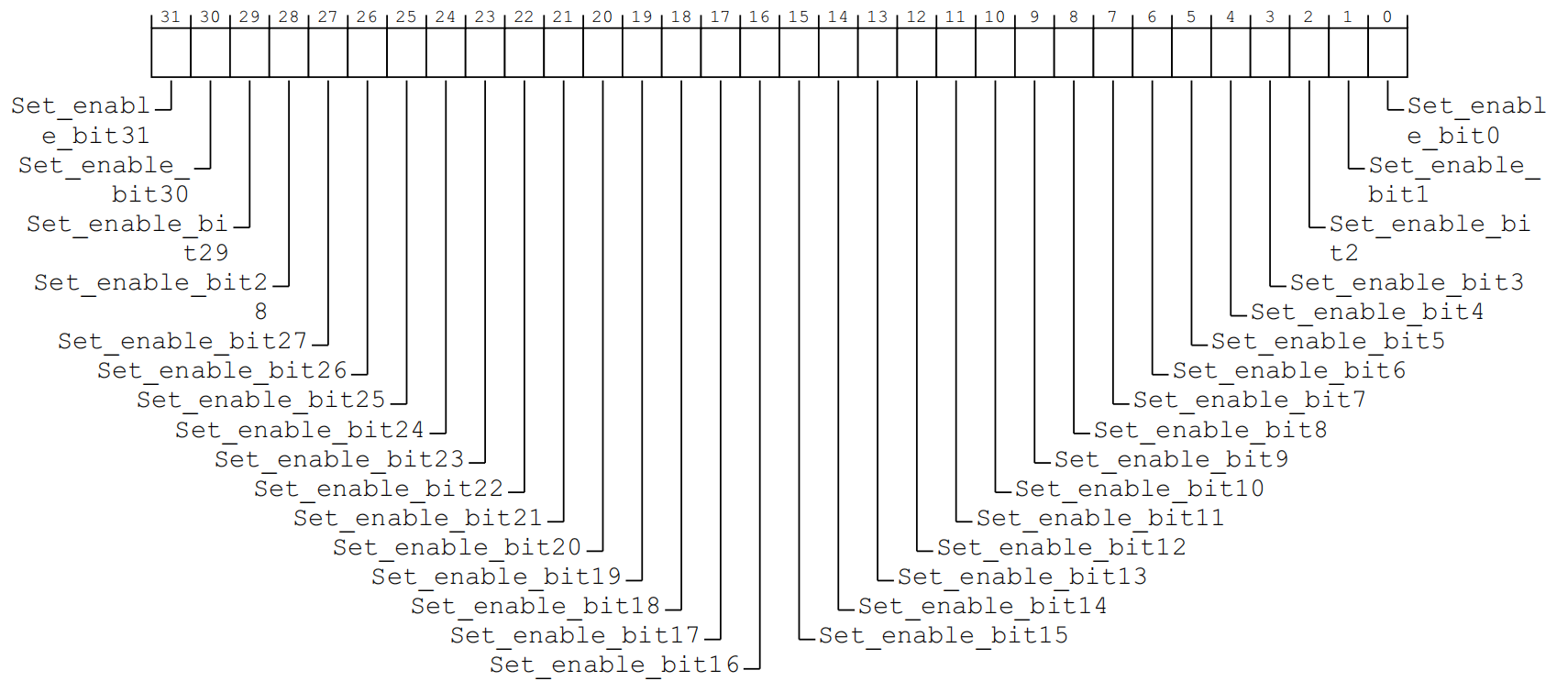

GICD_ISENABLER

Interrupt Set-Enable Registers,对应中断的 Enable 位控制寄存器。写 1 = 使能中断;写 0 不改变状态。读操作返回对应中断的 当前使能状态。

宽度:32-bit

每个寄存器覆盖 32 个中断 ID。

<n> 的范围:

- n=0 → ID [0–31]

- n=1 → ID [32–63]

- 以此类推

ID 计算方式: Interrupt ID = 32 * n + bit_position

GICD_ICENABLER

Interrupt Clear-Enable Registers 清除(禁用)中断的使能位。只要在 ICENABLER 中对某 bit 写 1,就会把该中断的“Enable”状态清 0,等效于 禁用此中断。

每个寄存器 32-bit,一共覆盖 32 个中断 ID。

<n> 的范围:

- n = 0 → 中断 ID 0–31

- n = 1 → ID 32–63

- …以此类推

计算公式: Interrupt ID = 32 * n + bit_position

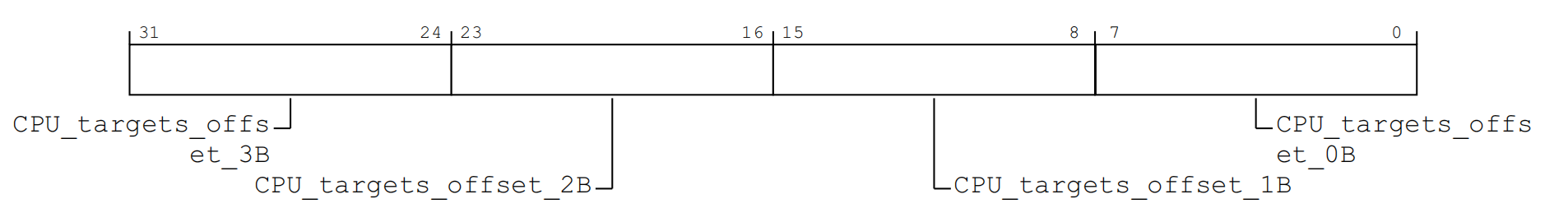

GICD_ITARGETSR

定义 中断 (SPI) 的目标 CPU(处理器接口)。

- 每个中断 ID 对应一个 8-bit 字段,指明该中断应该被路由到哪个 PE (Processing Element)。

- 只适用于 Shared Peripheral **Interrupts (SPIs, ID ≥ 32)**。

32-bit 寄存器。每个寄存器覆盖 4 个中断 ID。<n> 的计算方式:中断 ID = 4 * n + (0..3),每个中断用 8 位字段表示目标 CPU。

| Bits | 字段 | 描述 |

|---|---|---|

| [7:0] | CPU_targets0 | Interrupt ID = 4n |

| [15:8] | CPU_targets1 | Interrupt ID = 4n+1 |

| [23:16] | CPU_targets2 | Interrupt ID = 4n+2 |

| [31:24] | CPU_targets3 | Interrupt ID = 4n+3 |

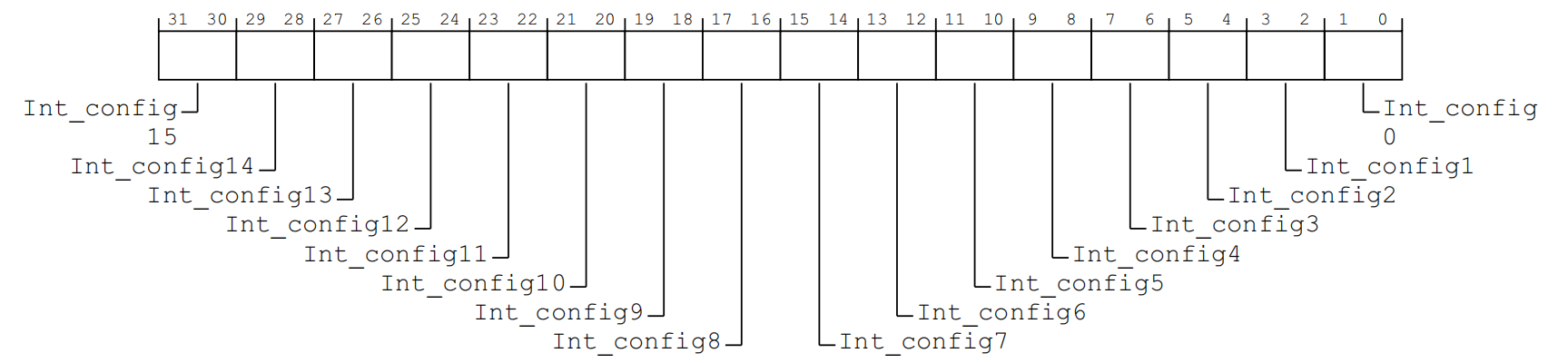

GICD_ICFGR

控制 中断触发方式:电平触发 (Level-sensitive) 还是边沿触发 (Edge-triggered)。

只适用于 PPI (ID16–31) 和 SPI **(ID ≥ 32)**。

- 32-bit 寄存器。

- 每个寄存器覆盖 16 个中断 ID。

- 每个中断占用 2 bit。

bit[1] (高位) = Trigger mode

- 0 = Level-sensitive

- 1 = Edge-triggered

bit[0] (低位) = Reserved (RES0),读为 0,写入忽略。

| Bits | 对应中断 |

|---|---|

| [1:0] | ID = 16n |

| [3:2] | ID = 16n+1 |

| [5:4] | ID = 16n+2 |

| … | … |

| [31:30] | ID = 16n+15 |

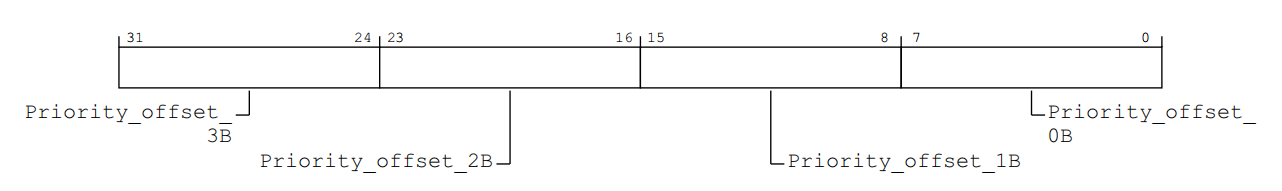

GICD_IPRIORITYR

- 控制 **每个中断的优先级 (Priority)**。优先级越低,数值越小,代表中断更重要。每个中断对应一个 8-bit 优先级字段。

| Bits | 字段 | 对应中断 |

|---|---|---|

| [7:0] | Priority0 | ID = 4n |

| [15:8] | Priority1 | ID = 4n+1 |

| [23:16] | Priority2 | ID = 4n+2 |

| [31:24] | Priority3 | ID = 4n+3 |

2.6.4 Redistributor寄存器

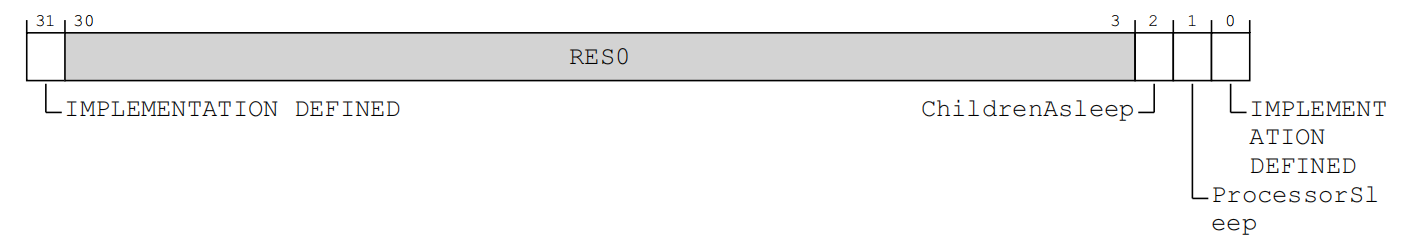

GICR_WAKER

- ChildrenAsleep, bit [2] (只读)

- 指示连接的处理器(PE)是否处于静止状态(quiescent)。

- 0b0:至少一个与 PE 关联的接口可能是活跃的(active)。

- 0b1:所有与 PE 关联的接口都处于静止状态(quiescent)。

- GIC 重置(GIC reset)时,此字段复位为 1(表示静止)

- ProcessorSleep, bit [1]

- 控制 Redistributor 是否发出 WakeRequest 信号,指示处理器(PE)是否进入低功耗状态。

- 0b0:PE 未处于低功耗状态,Redistributor 正常运行,处理中断。

- 0b1:PE 处于或正在进入低功耗状态,Redistributor 不向 CPU 接口传递中断,而是:

- 发出 WakeRequest 信号(通知电源管理单元)。

- 将到达的中断保持在挂起(Pending)状态,不传递到 CPU 接口。

- 注意:当 ProcessorSleep == 1 时,Redistributor 必须释放 CPU 接口上挂起的中断(通过 Release 命令)。

- GIC 重置时,此字段复位为 1(低功耗状态)。

- IMPLEMENTATION DEFINED, bit [0]

- 描述:由硬件实现定义,可能用于特定功能(例如额外的电源管理控制)。

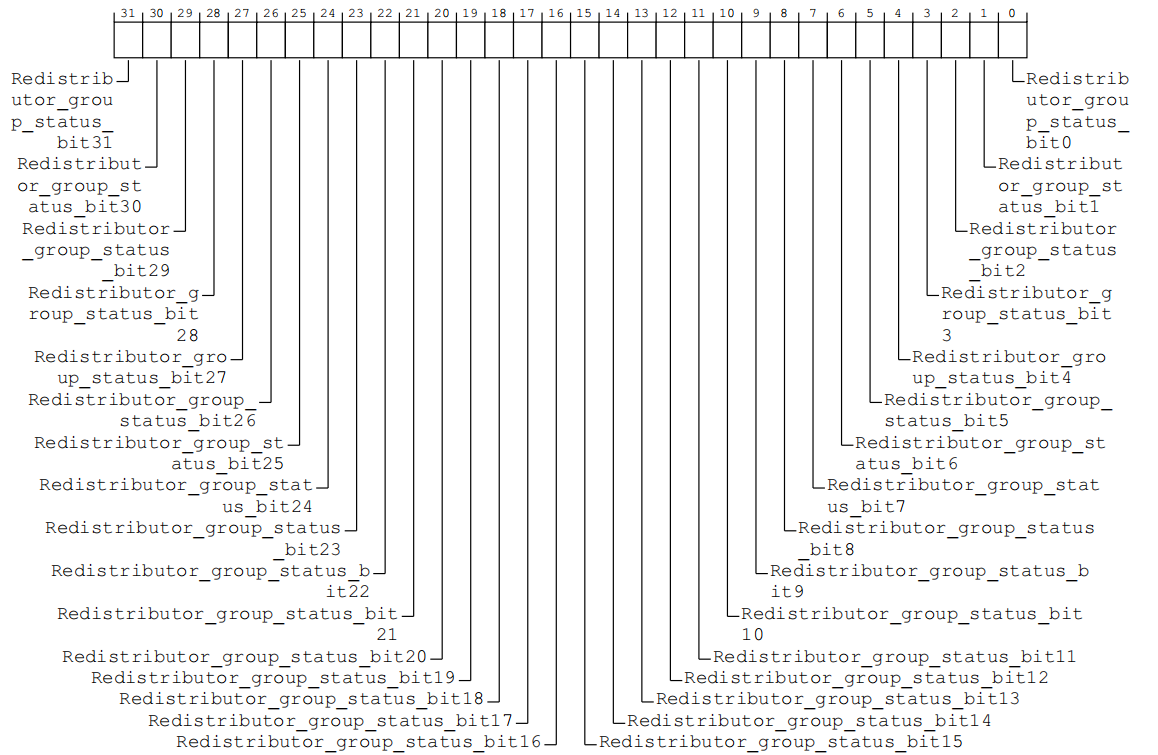

GICR_IGROUPR0

| 位(Bit) | 对应中断 ID | 读写属性 | 功能说明 |

|---|---|---|---|

| 31 ~ 0 | 31 ~ 0 | 读写 | 控制对应中断 ID 的中断组: - 0:中断归属 Group 0(通常为 “安全中断” 或 “EL1 必须处理的中断”,需通过 IRQ 异常向量处理) - 1:中断归属 Group 1(通常为 “非安全中断”,又细分为 Group 1S/1NS,分别对应安全态 EL1、非安全态 EL1/EL2 处理) |

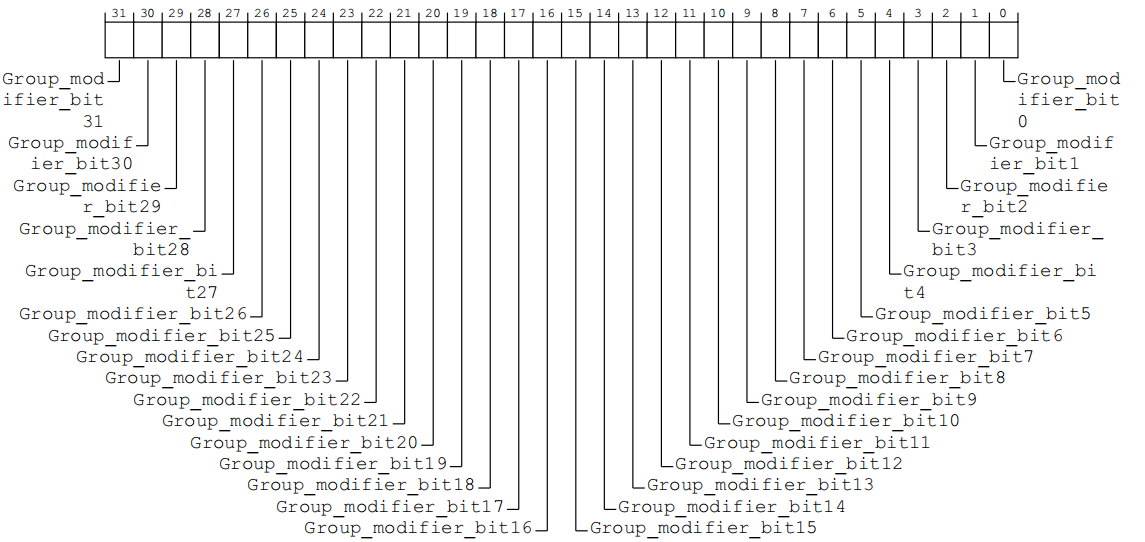

GICR_IGRPMODR0

GICR_IGRPMODR0 的核心是 “覆盖原始分组,强制切换到 Group 1”

| 位(Bit) | 对应中断 ID | 读写属性 | 功能说明(核心:修改 “有效分组”) |

|---|---|---|---|

| 31 ~ 0 | 31 ~ 0 | 读写 | 控制对应中断 ID 的 “组模式”,需结合 GICR_IGROUPR0(中断原始分组) 共同生效: - 0:中断的 “有效分组”= 原始分组(GICR_IGROUPR0 配置的 Group 0/1),无模式修改; - 1:中断的 “有效分组” 被强制改为 Group 1(无论 GICR_IGROUPR0 原始配置是 Group 0 还是 1 |

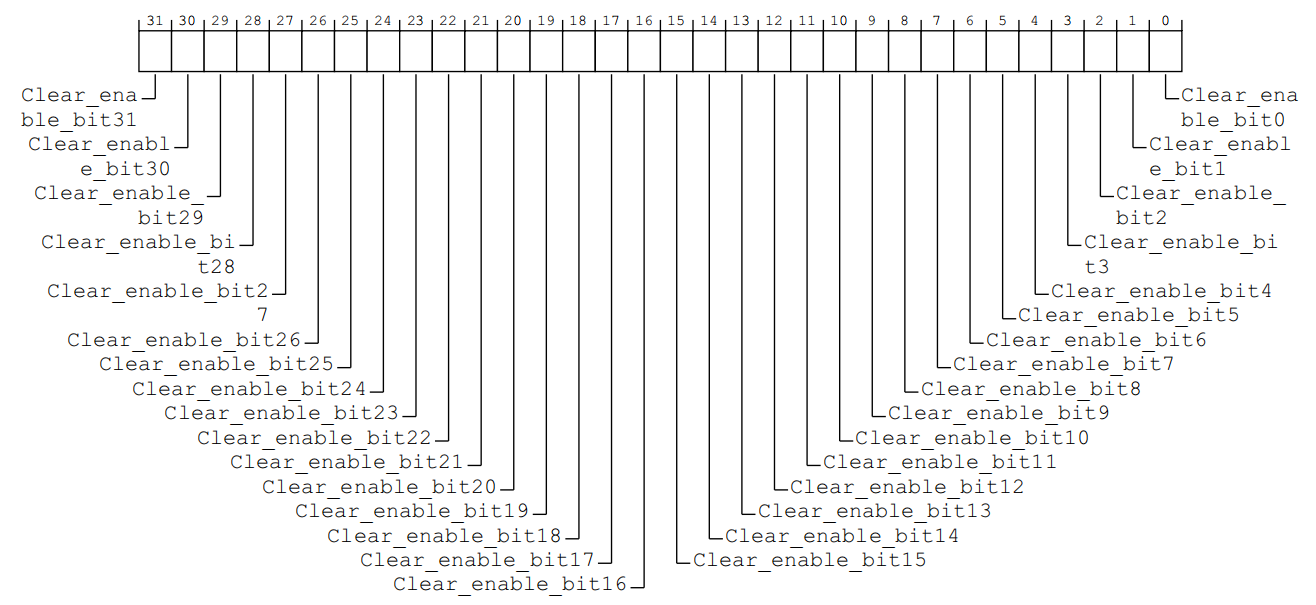

GICR_ICENABLER0

禁用(关闭)中断 ID 0~31 的私有中断(PPI/SGI)

GICR_ICENABLER0 专门用于 SGI (ID0–15) 和 PPI **(ID16–31)**。

宽度:32-bit

覆盖中断号:

- bit[0..15] → SGI0–SGI15

- bit[16..31] → PPI0–PPI15

| 位(Bit) | 对应中断 ID | 读写属性 | 功能说明(核心:触发中断禁用) |

|---|---|---|---|

| 31 ~ 0 | 31 ~ 0 | 仅写 | 控制对应中断 ID 的 “禁用” 动作,规则严格: - 写 1:立即禁用该中断 —— 即使中断当前处于 “待处理” 状态,也会被屏蔽,不再向 CPU 上报; - 写 0:无任何操作(无法通过写 0 “恢复启用”,启用需通过 GICR_ISENABLER0 寄存器) |

GICR_ICACTIVER0

清除(取消激活)中断 ID 0~31 的私有中断(PPI/SGI)的 “激活状态”,解决中断 “触发后持续上报” 的问题

- 当中断源(如定时器、传感器)产生触发信号,GIC 会将该中断标记为 “激活态”;

- 处于激活态的中断,会持续向 CPU 发起请求(直到被清除);

- 即使通过

GICR_ICENABLER0禁用中断,若中断已处于激活态,仍需先清除激活态,才能彻底停止上报。

GICR_ICACTIVER0 的核心作用,就是主动清除这个 “激活态”,让中断回到 “未激活” 状态。

| 位(Bit) | 对应中断 ID | 读写属性 | 功能说明(核心:清除激活态) |

|---|---|---|---|

| 31 ~ 0 | 31 ~ 0 | 仅写 | 控制对应中断 ID 的 “激活态清除” 动作,规则严格: - 写 1:立即清除该中断的 “激活态”—— 若中断当前处于激活状态,清除后会停止向 CPU 上报;若中断未激活,写 1 无效果; - 写 0:无任何操作(无法通过写 0 “恢复激活态”,激活态由中断源重新触发产生) |

GICR_ICPENDR0

清除(取消挂起)中断 ID 0~31 的私有中断(PPI/SGI)的 “挂起状态”

- 挂起态(Pending):中断源已触发请求,但 GIC 尚未向 CPU 发起 “激活上报”(可能因优先级不够、被屏蔽等),处于 “等待被激活” 的状态;

- 激活态(Active):中断已通过 GIC 向 CPU 上报,CPU 正在处理或准备处理,处于 “持续请求 CPU 响应” 的状态;

- 逻辑关系:多数中断需先进入 “挂起态”,满足条件后再进入 “激活态”;

GICR_ICPENDR0针对 “挂起态”,GICR_ICACTIVER0针对 “激活态”

| 位(Bit) | 对应中断 ID | 读写属性 | 功能说明(核心:清除挂起态) |

|---|---|---|---|

| 31 ~ 0 | 31 ~ 0 | 仅写 | 控制对应中断 ID 的 “挂起态清除” 动作,规则严格: - 写 1:立即清除该中断的 “挂起状态”—— 若中断当前处于挂起态,清除后不会再进入激活态;若中断未挂起(已激活或未触发),写 1 无效果; - 写 0:无任何操作(无法通过写 0 “恢复挂起态”,挂起态需中断源重新触发产生) |

GICR_ICFGR1

配置特定中断的触发类型,决定中断信号以何种方式(电平 / 边沿)被 GIC 识别。

寄存器共 32 位,采用 “2 位控制 1 个中断” 的映射规则,每 2 位对应 1 个中断 ID,具体位分配与含义如下:

| 寄存器位域 | 对应中断 ID | 位值含义(触发类型) |

|---|---|---|

| Bit[1:0] | ID 32 | 00 = 电平触发(Low-level) 01 = 边沿触发(Rising-edge) 10 = 边沿触发(Falling-edge) 11 = 双边沿触发(Rising & Falling) |

| Bit[3:2] | ID 33 | 同 Bit [1:0] |

| … | … | … |

| Bit[31:30] | ID 47 | 同 Bit [1:0] |

2.6.5 CPU interface寄存器

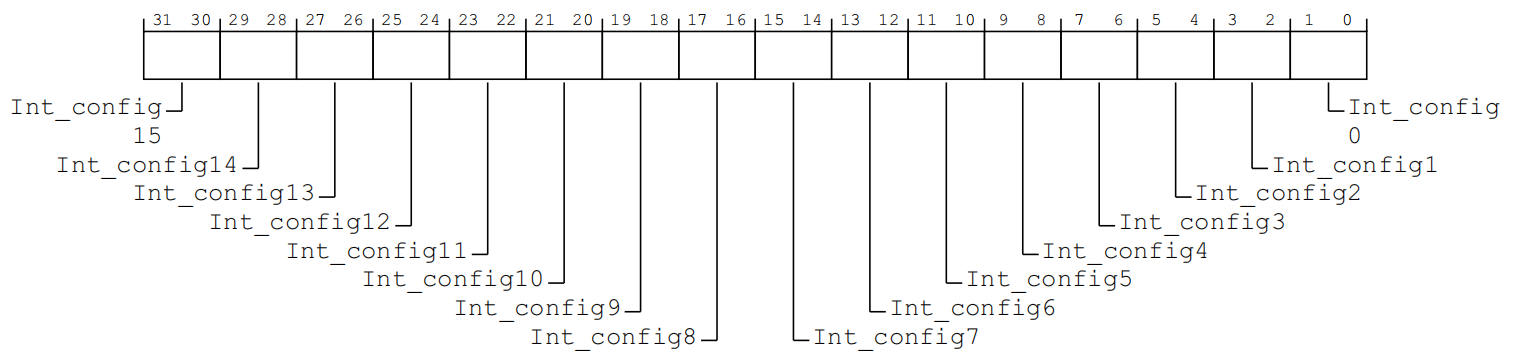

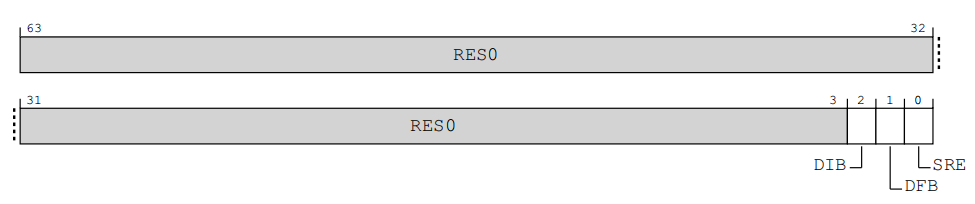

ICC_SRE_EL2

启用 EL2 对 GIC 系统寄存器的访问、配置中断虚拟化路由特性

| 位 | 字段名 | 描述 | 默认值 |

|---|---|---|---|

| [0] | SRE | System Register Enable:使能系统寄存器访问。0:禁用;1:启用。 | 0/1* |

| [1] | DFB | Disable FIQ Bypass:禁用 FIQ(Group 0)绕过。1:禁用绕过。 | 0 |

| [2] | DIB | Disable IRQ Bypass:禁用 IRQ(Group 1)绕过。1:禁用绕过。 | 0 |

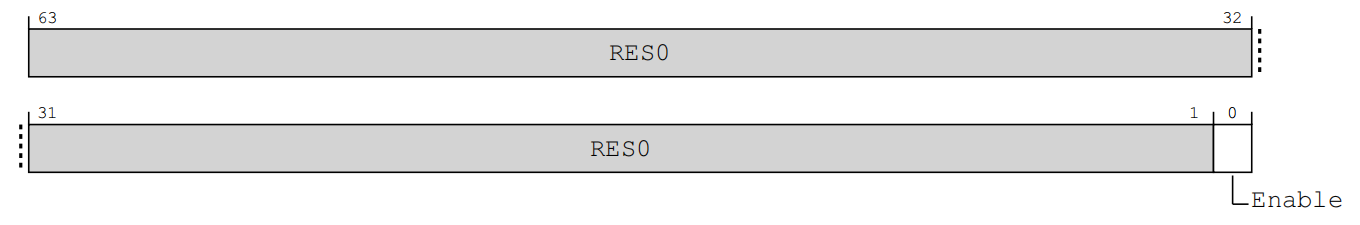

| [3] | Enable | Enable Lower ELs:允许较低异常级别(EL1/EL0)使用 GIC 系统寄存器。1:允许。 | 0 |

| [63:4] | RES0 | 保留,读为 0,写忽略(RAZ/WI)。 | 0 |

ICC_SRE_EL1

中断控制器系统寄存器使能寄存器,EL1

| 位 | 字段名 | 描述 | 默认值 |

|---|---|---|---|

| [0] | SRE | System Register Enable:使能系统寄存器访问。0:禁用;1:启用。 | 0/1* |

| [1] | DFB | Disable FIQ Bypass:禁用 FIQ(Group 0)绕过。1:禁用绕过。 | 0 |

| [2] | DIB | Disable IRQ Bypass:禁用 IRQ(Group 1)绕过。1:禁用绕过。 | 0 |

| [63:3] | RES0 | 保留,读为 0,写忽略(RAZ/WI)。 | 0 |

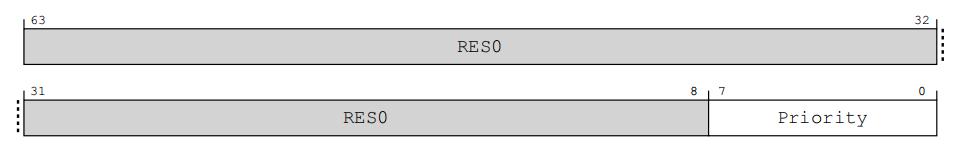

ICC_PMR_EL1

在 EL1设置中断优先级掩码(Priority Mask),控制哪些中断可以被 CPU 接口传递到处理器。只有小于Priority的中断可以被触发

| 位 | 字段名 | 描述 | 默认值 |

|---|---|---|---|

| [7:0] | Priority | 优先级掩码值。决定可传递的中断优先级(数值越小,优先级越高)。 | UNKNOWN* |

| [63:8] | RES0 | 保留,读为 0,写忽略(RAZ/WI)。 | 0 |

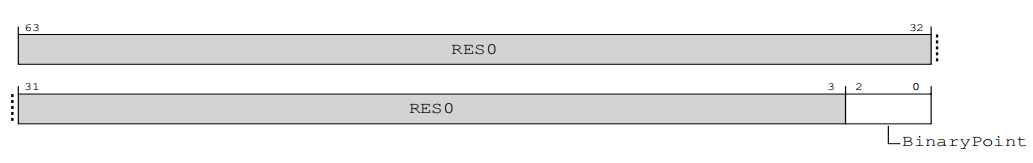

ICC_BPR1_EL1

用于在 EL1设置 Group 1 中断(通常为 IRQ,非安全中断)的二进制点(Binary Point),从而控制中断的优先级比较和抢占行为

| 位 | 字段名 | 描述 | 默认值 |

|---|---|---|---|

| [2:0] | BinaryPoint | 二进制点值(0–7)。决定优先级比较的分组方式。 | UNKNOWN* |

| [63:3] | RES0 | 保留,读为 0,写忽略(RAZ/WI)。 | 0 |

BinaryPoint:

- 3 位字段,值范围为 0x0 到 0x7,定义优先级值的二进制点位置。

- 优先级值(8 位,0x00–0xFF,数值越小优先级越高)被分为:

- 高位(抢占组):优先级值的左边部分(高 8 - BinaryPoint 位)。

- 低位(子优先级):优先级值的右边部分(低 BinaryPoint 位)。

- 中断抢占规则:

- 只有抢占组值(高位)小于当前运行中断的抢占组值时,新中断才能抢占。

- 子优先级(低位)用于同组内中断的排序,不影响抢占。

- 示例:

- 若 BinaryPoint = 0,优先级值全为抢占组,无子优先级,抢占最严格。

- 若 BinaryPoint = 3,优先级值的高 5 位为抢占组,低 3 位为子优先级。

- 若 BinaryPoint = 7,优先级值的高 1 位为抢占组,低 7 位为子优先级,抢占最宽松。

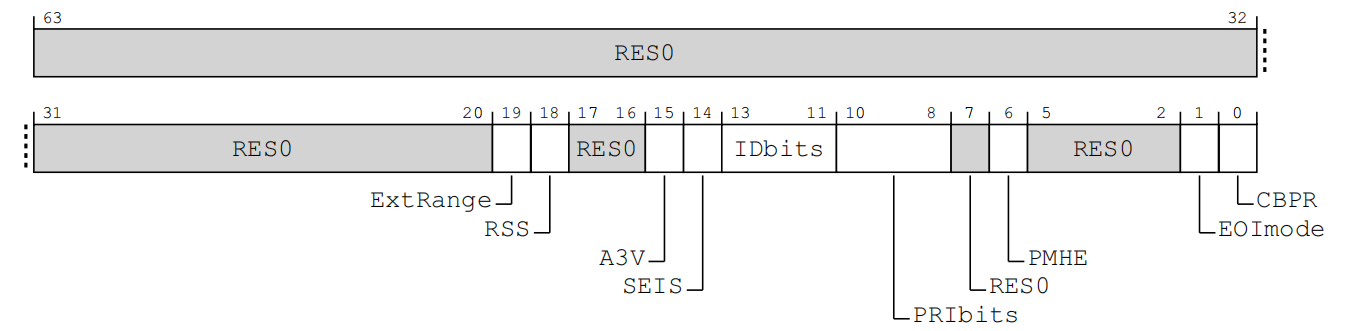

ICC_CTLR_EL1

| 字段名称 | 位域范围 | 读写属性 | 核心功能(文档原文定义) |

|---|---|---|---|

| ExtRange | Bit [19] | 只读(RO) | 标识 CPU 接口是否支持 1024~8191 范围的 INTID: - 0b0:不支持,若 IRI 转发此范围中断则行为 UNPREDICTABLE; - 0b1:支持,此范围 INTID 均需执行去激活操作。 EL3 关联:若 EL3 实现,此位是 ICC_CTLR_EL3.ExtRange 的别名(此前未提及 EL3 别名关系)。 |

| RSS | Bit [18] | 只读(RO) | 范围选择器支持(Targeted SGI 的 Affinity 0 范围): - 0b0:仅支持 Affinity 0 为 0 |

| A3V | Bit [15] | 只读(RO) | Affinity 3 有效性: - 0b0:CPU 接口仅支持 SGI 生成寄存器中 Affinity 3 为 0 的值; - 0b1:支持 Affinity 3 为非 0 的值。 EL3 关联:若 EL3 实现,此位是 ICC_CTLR_EL3.A3V 的别名(此前仅提及 “4 级 affinity 支持”,未明确 “SGI 生成寄存器关联”)。 |

| SEIS | Bit [14] | 只读(RO) | SEI(System Error Interrupt)支持: - 0b0:CPU 接口不支持本地生成 SEI; - 0b1:支持本地生成 SEI。 EL3 关联:若 EL3 实现,此位是 ICC_CTLR_EL3.SEIS 的别名(此前完全遗漏该字段)。 |

| IDbits | Bits [13:11] | 只读(RO) | 物理中断标识位数(INTID 位数): - 0b000:16 位 INTID; - 0b001:24 位 INTID; 其他值保留。 EL3 关联:若 EL3 实现,此字段是 ICC_CTLR_EL3.IDbits 的别名(此前未明确 “仅 0b000/0b001 有效”)。 |

| PRIbits | Bits [10:8] | 只读(RO) | 优先级位数(实现的优先级位数减 1): - 若支持两个 Security 状态:至少 5 位(32 级优先级,PRIbits≥0b100); - 若支持单个 Security 状态:至少 4 位(16 级优先级,PRIbits≥0b011)。 关键约束:此字段值决定 ICC_BPR0_EL1 的最小值(此前未提及 “优先级位数与 BPR 最小值关联”)。 |

| PMHE | Bit [6] | 读写 / 只读(R/W/RO) | 优先级掩码提示使能(控制 ICC_PMR_EL1 是否作为中断分发的提示): - 0b0:禁用; - 0b1:启用。 读写属性约束(文档 12-235): - EL3 实现时:GICD_CTLR.DS=0 → 只读;DS=1 → 可写; - EL3 未实现时:IMPLEMENTATION DEFINED(只读则 RAZ/WI 或 RAO/WI,可写则复位为 0)。 |

| EOImode | Bit [1] | 只读(RO) | EOI 模式(当前 Security 状态): - 0b0:ICC_EOIR0/1_EL1 同时完成 “优先级下降 + 中断去激活”,访问 ICC_DIR_EL1 行为 UNPREDICTABLE; - 0b1:ICC_EOIR0/1_EL1 仅完成优先级下降,需 ICC_DIR_EL1 完成去激活。 |

| CBPR | Bit [0] | 读写 / 只读(R/W/RO) | 公共二进制点寄存器(控制 Group 0/1 中断是否共享 BPR 寄存器): - 0b0:Group 0 用 ICC_BPR0_EL1,Group 1 用 ICC_BPR1_EL1; - 0b1:Group 0/1 均用 ICC_BPR0_EL1。 读写属性约束(文档 12-235): - EL3 实现时:DS=0 → 只读;DS=1 → 可写; - EL3 未实现时:可写 |

EOI Mode 的本质是规定 CPU 接口处理 “中断结束” 操作时,是否将 “优先级下降” 与 “中断去激活” 两个动作分离:

- “优先级下降”:指 CPU 接口将当前运行优先级(由

ICC_RPR_EL1记录)恢复为中断处理前的状态,允许低优先级中断被重新响应; - “中断去激活”:指清除中断的 “活跃状态”(仅适用于 SGIs、PPIs、SPIs,LPIs 无活跃状态),使中断可再次进入 “待处理(Pending)” 状态以响应新的触发。

文档明确:EOI Mode 的配置仅对物理中断(Group 0/Group 1)生效,且与 ICC_EOIR0_EL1(Group 0 中断)、ICC_EOIR1_EL1(Group 1 中断)、ICC_DIR_EL1(中断去激活寄存器)的使用强关联。

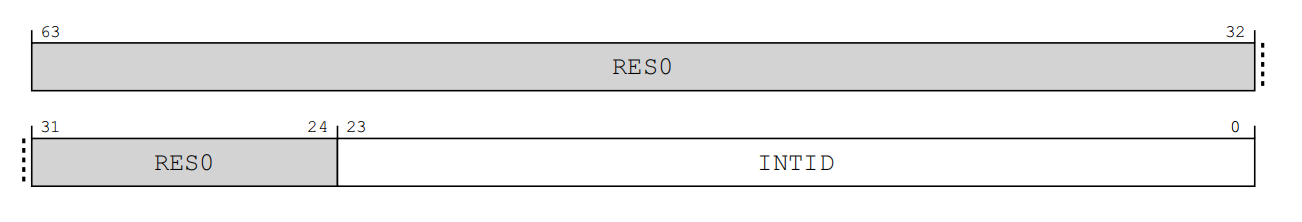

ICC_IGRPEN1_EL1

| 位(Bit) | 名称 | 读写属性 | 功能说明(Group 1 中断的全局使能控制) |

|---|---|---|---|

| 0 | Enable | 读写 | 控制 EL1 对 Group 1 中断的响应能力: - 1:使能 ——EL1 可接收并响应 Group 1 中断(符合路由规则的情况下); - 0:禁用 ——Group 1 中断即使触发,也不会送达 EL1(会被 CPU 接口层屏蔽)。 |

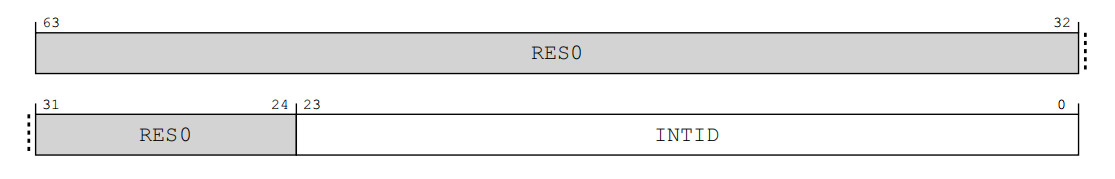

ICC_IAR1_EL1

用于从 GIC CPU 接口获取当前最高优先级中断的标识(Interrupt ID, INTID)。它是在处理 Group 1 中断(通常为 IRQ)时读取的寄存器,配合其他寄存器(如 ICC_EOIR1_EL1 和 ICC_DIR_EL1)完成中断的生命周期管理

- 简单来说就是获取当前最高优先级的中断ID,然后cpu会进行处理

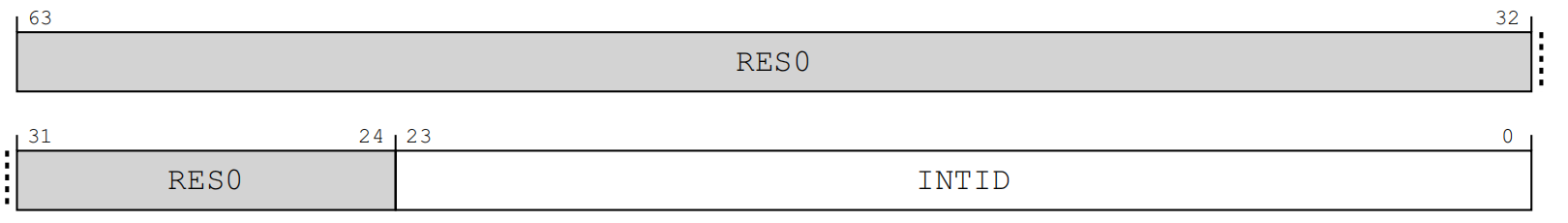

ICC_DIR_EL1

允许软件显式地将一个中断从 Active 状态清除(Deactivate)

ICC_EOIR1_EL1

用于 结束 (End) 一个 Group1 中断的处理。软件在完成中断服务例程后,必须写入此寄存器,把对应中断标记为 “EOI”

2.6.6 Virtual interface寄存器

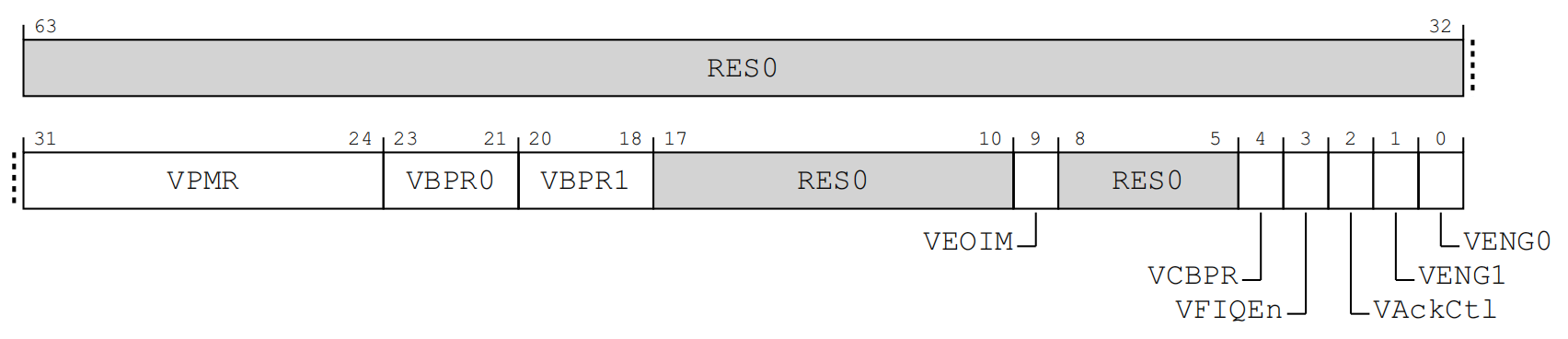

ICH_VMCR_EL2

- ICH_VMCR_EL2 模拟客户机的 ICC_CTLR_EL1, ICC_PMR_EL1, ICC_BPR0_EL1, ICC_BPR1_EL1 等寄存器,允许 Hypervisor 配置虚拟中断的优先级、抢占模式、使能状态等。

- 它控制虚拟 GIC 的行为,确保客户机看到一个虚拟 CPU 接口,而实际中断由 Hypervisor 处理。

ICH_HCR_EL2

En [0]:虚拟 CPU 接口总使能。为 0 时不产生任何虚拟/维护中断,读取 GICV_IAR/AIAR 返回伪中断 ID;注:当 SCR_EL3.{NS,EEL2}=={0,0} 时此位为 RES0;暖复位为 0

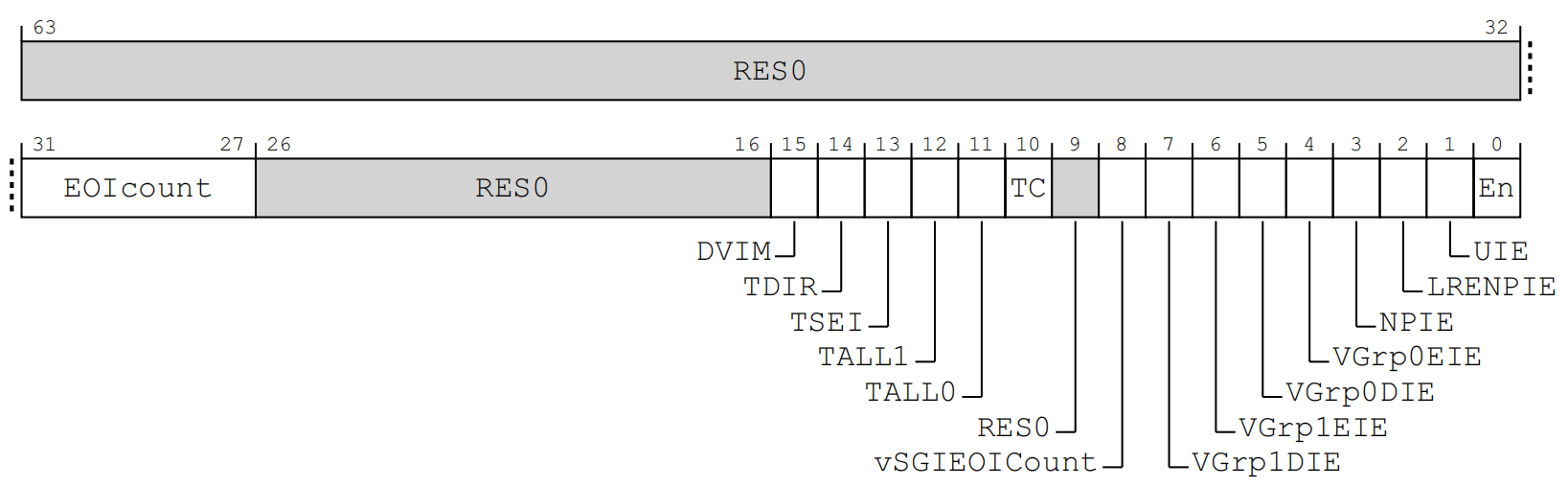

ICH_VTR_EL2

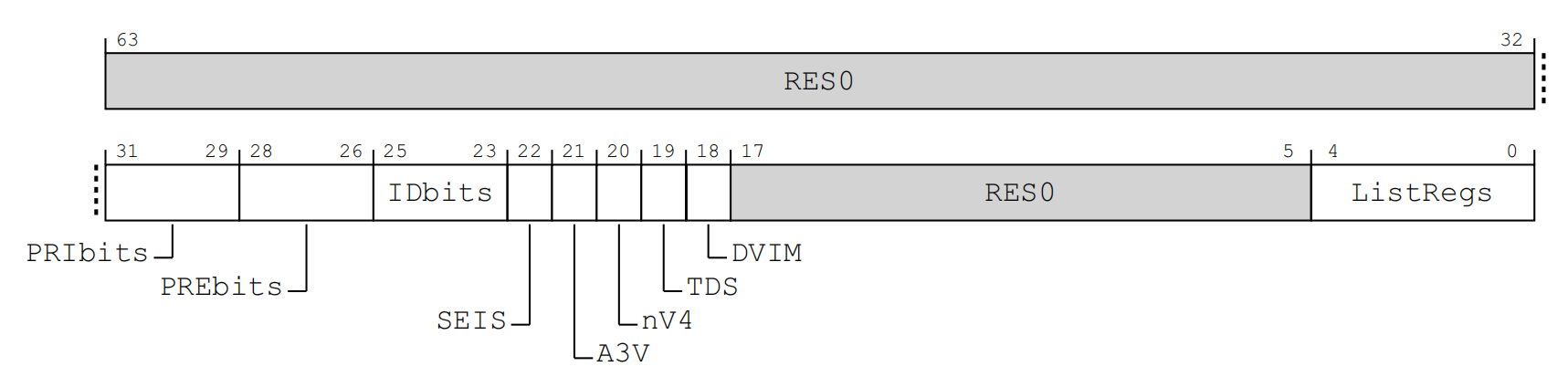

报告虚拟化 GIC(VGIC)的能力,包括虚拟优先级位数、可抢占位数、可编码的虚拟中断 ID 位宽、是否支持 SEI、是否支持 Aff3、是否支持直注入屏蔽等,以及 List Register(LR)数量。

- [63:32]:RES0。

- PRIbits [31:29]:虚拟优先级位数减 1。实现至少 5 个优先级位(≥32 级优先级)。该字段是 ICV_CTLR_EL1.PRIbits 的别名。实现可选值范围

0b100..0b110。RO。 - PREbits [28:26]:虚拟可抢占(preemption)位数减 1。至少 5 位;且 PREbits ≤ PRIbits;决定 ICH_VMCR_EL2.VBPR0 的最小值。实现可选值

0b000..0b110。RO。 - IDbits [25:23]:虚拟中断 ID 位数;实现可选值:

0b000 → 16 位,0b001 → 24 位;其余值保留。该字段是 ICV_CTLR_EL1.IDbits 的别名。RO。 - SEIS [22]:SEI 支持;

1=支持,0=不支持;别名 ICV_CTLR_EL1.SEIS。RO。 - A3V [21]:Affinity level 3 有效;

1=SGI 产生寄存器支持非零 Aff3;别名 ICV_CTLR_EL1.A3V。RO。 - nV4 [20]:不支持虚拟中断直注入标志;

0=支持直注入,1=不支持直注入;在 GICv3 中仅允许取值 1。RO。 - TDS [19]:对 EL1 写 ICV_DIR_EL1 的单独陷入支持;

1=实现支持 ICH_HCR_EL2.TDIR(由 FEAT_GICv3_TDIR 引入)。RO。 - DVIM [18]:对“直接注入的虚拟中断”的屏蔽支持;

1=支持,0=不支持。在实现了 Realm Management Extension (RME) 的 PE 上,该字段 RAO/WI;字段访问属性为 RO。 - [17:5]:RES0。

- ListRegs [4:0]:实现的 List Register 数量减 1。实现可选值范围

0b00000..0b01111。RO。> 例如读到0b01111表示 实现了 16 个 LR。

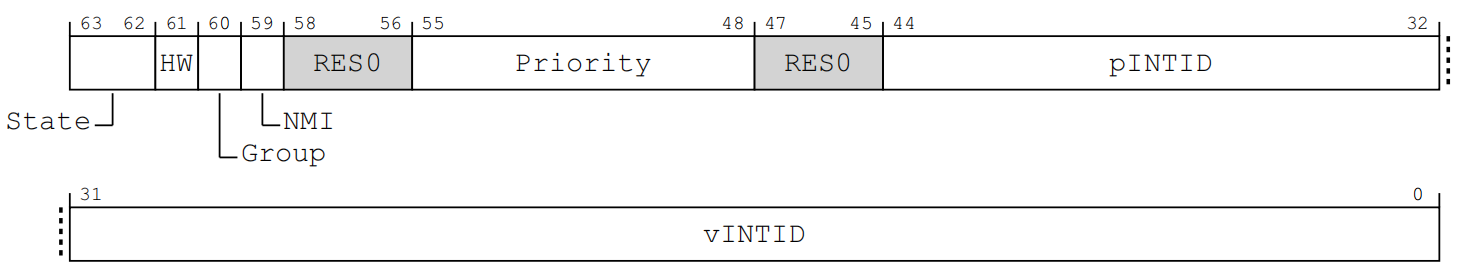

ICH_LR_EL2

该寄存器为虚拟 CPU 接口(virtual Processing Element, vPE)提供中断上下文信息。它充当虚拟中断的缓存,用于存储待处理(pending)、激活(active)或激活且待处理(active and pending)的虚拟中断信息。这有助于模拟硬件中断处理行为,使非虚拟化的操作系统能够像在物理环境中一样处理中断。在虚拟化环境中,Hypervisor 通过切换这些寄存器来管理虚拟机的中断上下文。

ARMv8 GIC(Generic Interrupt Controller)架构支持多个列表寄存器(List Registers),每个寄存器存储一个虚拟中断的上下文信息(如状态、优先级、虚拟/物理中断 ID 等)。

n 是一个索引值,范围通常从 0 到 15(具体数量由硬件实现定义,可通过 ICH_VTR_EL2 寄存器的 LRmax 字段查询,实际最大值可能小于 16)。

每个 ICH_LR

| 位范围 | 字段名 | 访问类型 | 描述 |

|---|---|---|---|

| [63:62] | State | RW | 中断状态: - 0b00:无效/非激活(Invalid/Inactive) - 0b01:待处理(Pending) - 0b10:激活(Active) - 0b11:激活且待处理(Active and Pending) GIC 在中断生命周期中更新此字段。复位值为 UNKNOWN。 |

| [61] | HW | RW | 指示虚拟中断是否映射到硬件中断: - 0b0:软件中断(Software,不在停用时通知 Distributor) - 0b1:硬件中断(Hardware,使用 pINTID 发送停用请求,对应 ICC_EOIR0/1_EL1 或 ICC_DIR_EL1,取决于 ICH_VMCR_EL2.VEOIM) 复位值为 UNKNOWN。 |

| [60] | Group | RW | 中断组: - 0b0:Group 0(作为虚拟 IRQ/FIQ 信号,根据 ICH_VMCR_EL2.VFIQEn 启用,由 VENG0 控制) - 0b1:Group 1(作为虚拟 IRQ 信号,由 VENG1 控制) 抢占由 ICC_BPR1_EL1 或 ICH_LR |

| [59:56] | RES0 | - | 保留位,必须为 0。 |

| [55:48] | Priority | RW | 中断优先级。位宽实现定义(至少 5 位,未实现的高位从 [48] 开始为 RES0)。复位值为 UNKNOWN。 |

| [47:45] | RES0 | - | 保留位,必须为 0。 |

| [44:32] | pINTID | RW | 物理中断 ID(Physical INTID)。当 HW=1 时,用于向 Distributor 发送停用请求。当 HW=0 时,部分位有特定用途(如位[19] 用于 EOI 维护,位[18:13] 应为 0,位[12:10] 用于 SGI 的请求 PE,如果 vINTID 为 0-15)。复位行为 UNKNOWN。 |

| [31:0] | vINTID | RW | 虚拟中断 ID(Virtual INTID)。持有虚拟中断编号,大小由 ICH_VTR_EL2.IDbits 决定。 |

![ARM64-Trust-Firmware[3]-BL1解析](/2026/01/24/ARM64-Trust-Firmware-3-BL1%E8%A7%A3%E6%9E%90/17692290470595.png)

![ARM64-Trust-Firmware[2]-启动ATF](/2026/01/24/ARM64-Trust-Firmware-2-%E5%90%AF%E5%8A%A8ATF/17692287555201.png)

![ARM64-Trust-Firmware[1]-ARM安全架构](/2026/01/24/ARM64-Trust-Firmware-1-ARM%E5%AE%89%E5%85%A8%E6%9E%B6%E6%9E%84/17692284856153.png)